Altera Arria V Hard IP for PCI Express User Manual

Page 11

Chapter 1: Datasheet

1–3

Features

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

f

The purpose of the Arria V Hard IP for PCI Express User Guide is to explain how to use

the Arria V Hard IP for PCI Express and not to explain the PCI Express protocol.

Although there is inevitable overlap between these two purposes, this document

should be used in conjunction with an understanding of the following PCI Express

specifications

Transaction Layer Packet Types (TLP)

(3)

■

Memory Read Request

■

Memory Read Request-Locked

■

Memory Write Request

■

I/O Read Request

■

I/O Write Request

■

Configuration Read Request

(Root Port)

■

Configuration Write Request

(Root Port)

■

Message Request

■

Message Request with Data

Payload

■

Completion without Data

■

Completion with data

■

Completion for Locked Read

without Data

■

Memory Read Request

■

Memory Write Request

■

Configuration Read Request

(Root Port)

■

Configuration Write Request

(Root Port)

■

Message Request

■

Message Request with Data

Payload

■

Completion without Data

■

Completion with Data

■

Memory Read Request (single

dword)

■

Memory Write Request (single

dword)

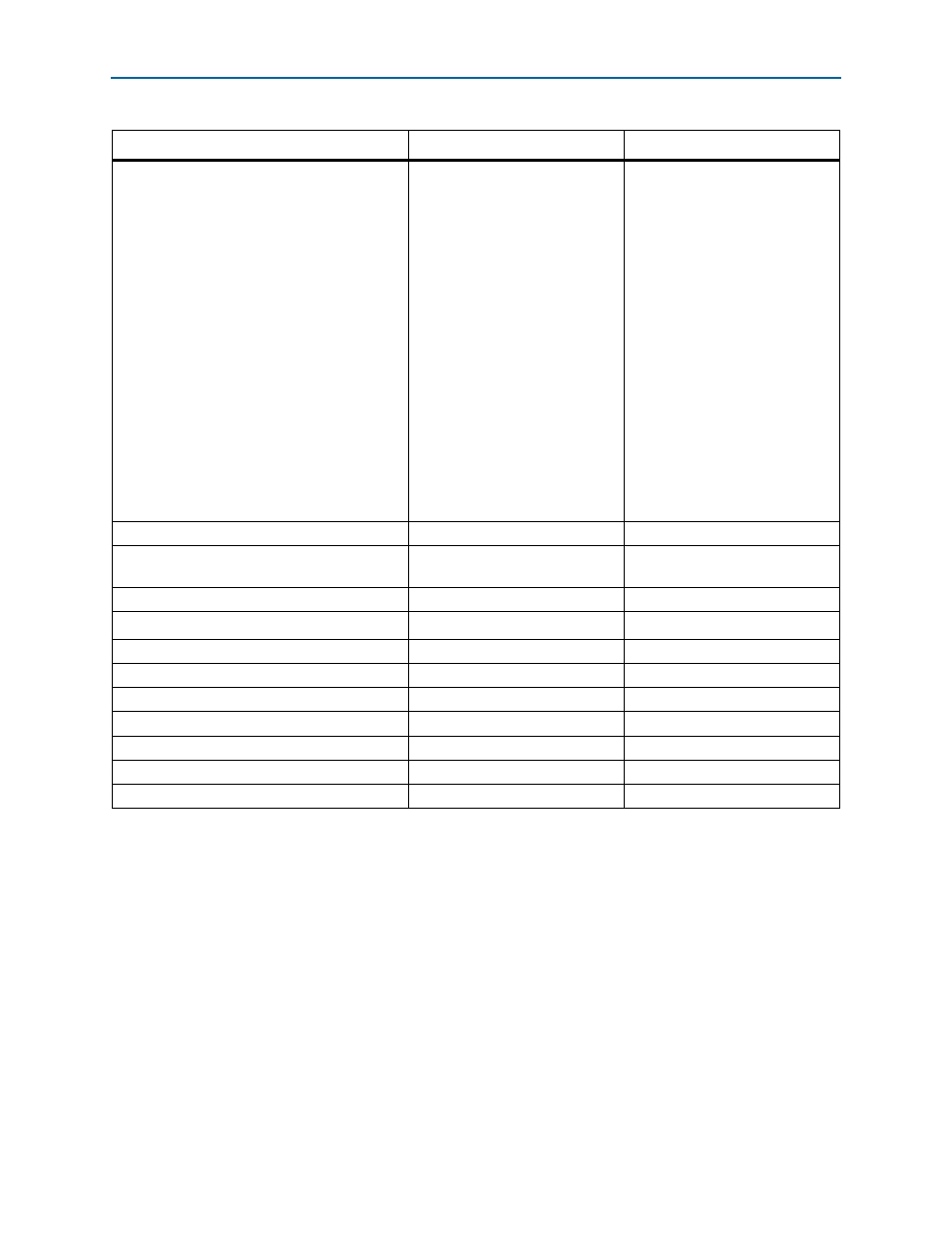

Maximum payload size

128–512 bytes

128–256 bytes

Number of tags supported for non-posted

requests

32 or 64

8

62.5 MHz clock

Supported

Supported

Multi-function

Supports up to 8 functions

Supports single function only

Polarity inversion of PIPE interface signals

Supported

Supported

ECRC forwarding on RX and TX

Supported

Not supported

Expansion ROM

Supported

Not supported

Number of MSI requests

16

1, 2, 4, 8, or 16

MSI-X

Supported

Supported

Multiple MSI, MSI-X, and INTx

Not Supported

Supported

Legacy interrupts

Supported

Supported

Notes to

Table 1–1

:

(1) Not recommended for new designs.

(2) ×2 is supported by down training from ×4 or ×8 lanes.

(3) Refer to

Appendix A, Transaction Layer Packet (TLP) Header Formats

for the layout of TLP headers.

Table 1–2. Differences in Features Available Using the Avalon-MM and Avalon-ST Interfaces (Part 2 of 2)

Feature

Avalon-ST Interface

Avalon-MM Interface