Avalon-mm hard ip for pci express, Avalon-mm hard ip for pci express –42 – Altera Arria V Hard IP for PCI Express User Manual

Page 140

7–42

Chapter 7: IP Core Interfaces

Avalon-MM Hard IP for PCI Express

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

Avalon-MM Hard IP for PCI Express

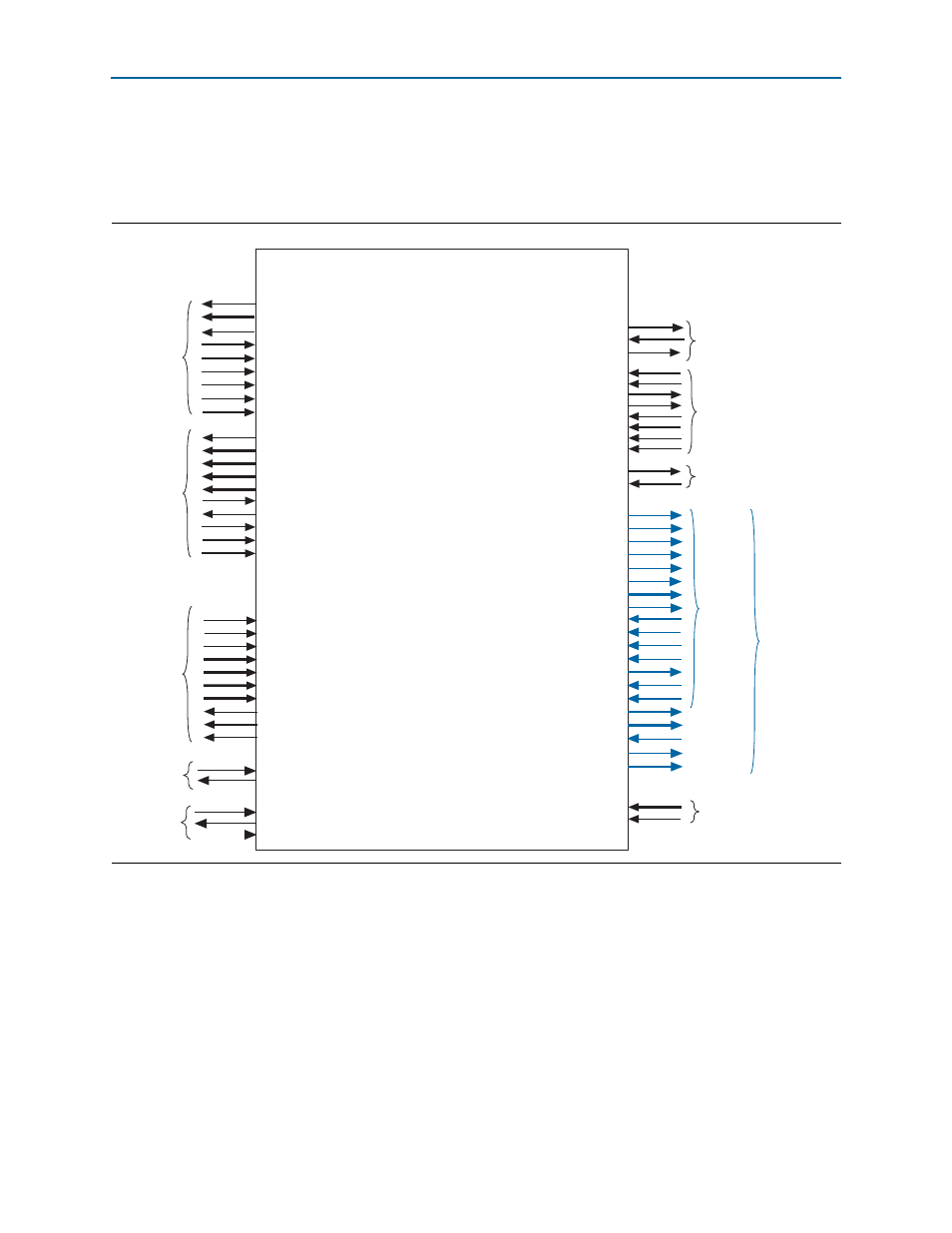

Figure 7–34

illustrates the signals of the full-featured Arria V Hard IP for PCI Express

using the Avalon-MM interface available in the Qsys design flow.

Figure 7–34. Signals in the Qsys Full-Featured Avalon-MM Arria V Hard IP for PCI Express

tx_out0[

:0]

rx_in0[

:0]

1-Bit Serial

CraReadData_o[31:0]

CraWaitRequest_o

CraByteEnable_i[3:0]

CraChipSelect_i

CraAddress_i[11:0]

CraRead

CraWrite

CraWriteData_i[31:0]

TxsWriteData[

-1:0]_i

TxsBusrtCount[6 or 5:0]_i

TxsChipSelect_i

TxsRead_i

TxsWrite_i

TxsAddress[

TxsByteEnable[

TxsReadDataValid_o

TxsReadData[

-1:0]_o

TxsWaitRequest_o

32-Bit

Avalon-MM

CRA

Slave Port

(Optional)

64-Bit

Avalon-MM TX

Slave Port

Avalon-MM Hard IP for PCI Express

(Full-Featured Qsys)

Test

Interface

test_in[31:0]

simu_mode_pipe

RxmWrite_

RxmAddress_

RxmWriteData_

-1:0]

RxmByteEnable_

RxmBurstCount_

RxmWaitRequest_

RxmRead_

RxmReadData_

-1:0]_i

RxmReadDataValid_

RxmIrq[

64-Bit

Avalon-MM TX

Master Port

reconfig_fromxcvr[

reconfig_toxcvr[

busy_xcvr_reconfig

reconfig_mgmt_address[6:0]

reconfig_mgmt_read

reconfig_mgmt_readdata[31:0]

reconfig_mgmt_waitrequest

reconfig_mgmt_write

reconfig_mgmt_writedata[31:0]

mgmt_rst_reset

mgmt_clk_clk

Transceiver

Reconfiguration

Reconfiguration

Management

Interface

txdatak0

txdata0[7:0]

txdetectrx0

txelectidle0

rxpolarity0

txcompl0

powerdown0[1:0]

tx_deemph0

rxdatak0

rxdata0[7:0]

rxvalid0

phystatus0

eidleinfersel0[2:0]

rxelectidle0

rxstatus0[2:0]

sim_ltssmstate[4:0]

sim_pipe_rate0[1:0]

sim_pipe_pclk_in

txswing0

txmargin0[2:0]

PIPE Interface

Simulation Only

8-Bit PIPE

Clocks

npor

nreset_status

pin_perstn

Reset &

Lock Status

refclk

coreclkout _hip

CraIrq_o