Altera Arria V Hard IP for PCI Express User Manual

Page 214

14–4

Chapter 14: Error Handling

Transaction Layer Errors

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

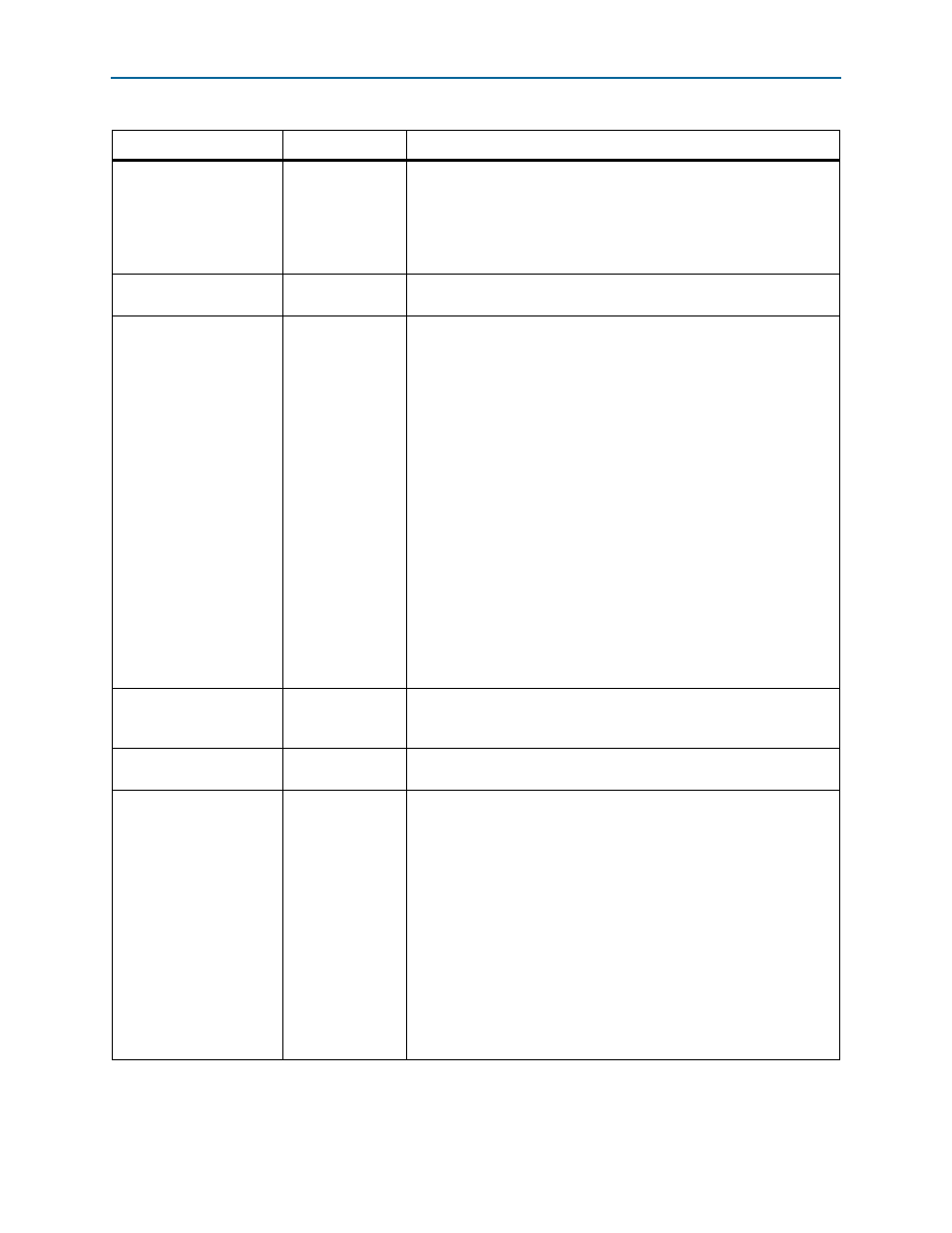

Completion timeout

Uncorrectable

(non-fatal)

This error occurs when a request originating from the Application Layer

does not generate a corresponding completion TLP within the

established time. It is the responsibility of the Application Layer logic to

provide the completion timeout mechanism. The completion timeout

should be reported from the Transaction Layer using the

cpl_err[0]

signal.

Completer abort

Uncorrectable

(non-fatal)

The Application Layer reports this error using the

cpl_err[2]

signal

when it aborts receipt of a TLP.

Unexpected completion

Uncorrectable

(non-fatal)

This error is caused by an unexpected completion transaction. The Hard

IP block handles the following conditions:

■

The Requester ID in the completion packet does not match the

Configured ID of the Endpoint.

■

The completion packet has an invalid tag number. (Typically, the tag

used in the completion packet exceeds the number of tags specified.)

■

The completion packet has a tag that does not match an outstanding

request.

■

The completion packet for a request that was to I/O or Configuration

Space has a length greater than 1 dword.

■

The completion status is Configuration Retry Status (CRS) in

response to a request that was not to Configuration Space.

In all of the above cases, the TLP is not presented to the Application

Layer; the Hard IP block deletes it.

The Application Layer can detect and report other unexpected

completion conditions using the

cpl_err[2]

signal. For example, the

Application Layer can report cases where the total length of the received

successful completions do not match the original read request length.

Receiver overflow

Uncorrectable

(fatal)

This error occurs when a component receives a TLP that violates the FC

credits allocated for this type of TLP. In all cases the hard IP block

deletes the TLP and it is not presented to the Application Layer.

Flow control protocol error

(FCPE)

Uncorrectable

(fatal)

This error occurs when a component does not receive update flow

control credits with the 200

μ

s limit.

Malformed TLP

Uncorrectable

(fatal)

This error is caused by any of the following conditions:

■

The data payload of a received TLP exceeds the maximum payload

size.

■

The

TD

field is asserted but no TLP digest exists, or a TLP digest

exists but the

TD

bit of the PCI Express request header packet is not

asserted.

■

A TLP violates a byte enable rule. The Hard IP block checks for this

violation, which is considered optional by the PCI Express

specifications.

■

A TLP in which the

type

and

length

fields do not correspond with

the total length of the TLP.

■

A TLP in which the combination of format and type is not specified by

the PCI Express specification.

Table 14–4. Errors Detected by the Transaction Layer (Part 2 of 3)

Error

Type

Description