Msi-x table offset bir – Altera Arria V Hard IP for PCI Express User Manual

Page 178

8–24

Chapter 8: Register Descriptions

Correspondence between Configuration Space Registers and the PCIe Spec 2.1

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

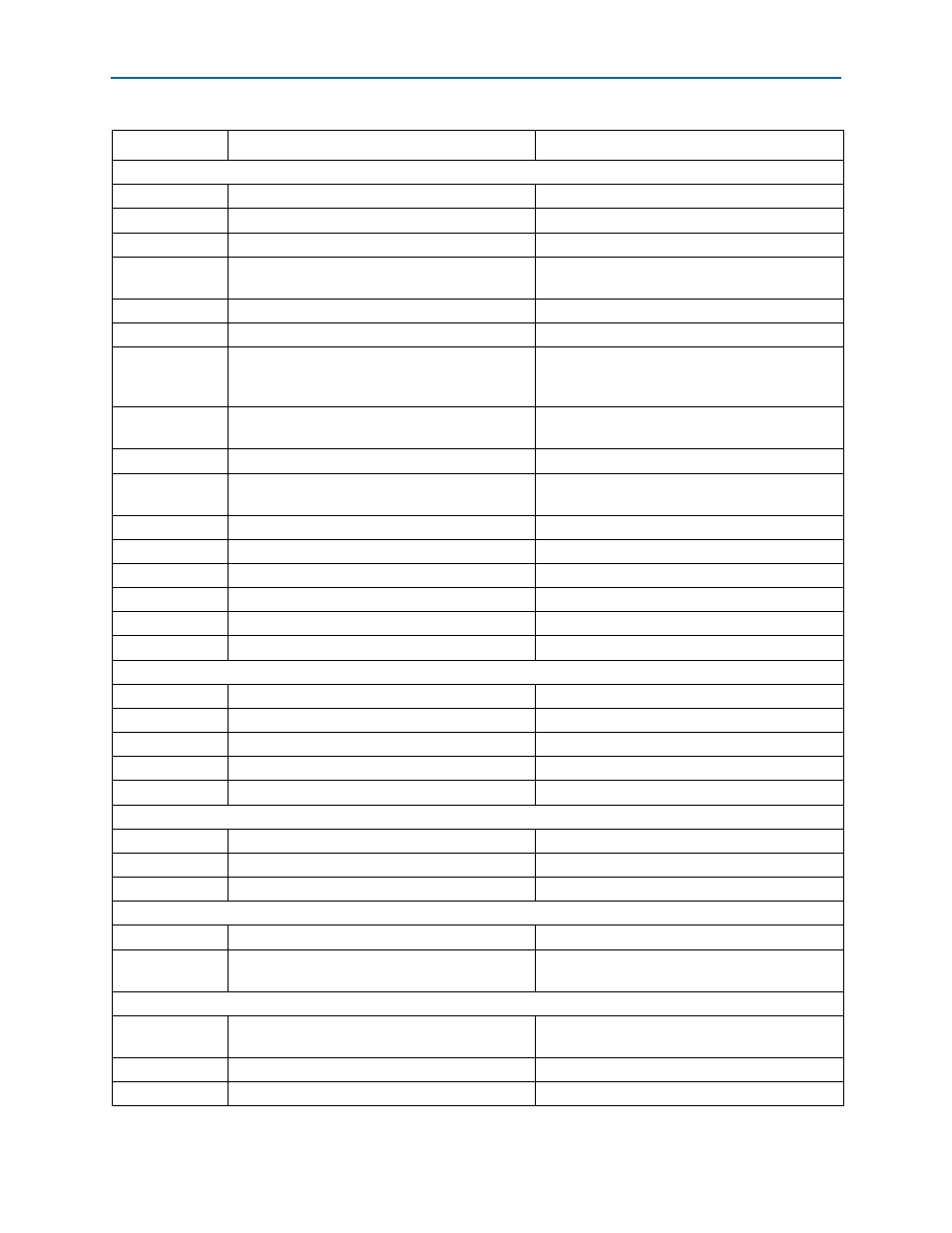

Table 6-3.

PCI Type 1 Configuration Space Header (Root Ports)

0x000

Device ID Vendor ID

Type 1 Configuration Space Header

0x004

Status Command

Type 1 Configuration Space Header

0x008

Class Code Revision ID

Type 1 Configuration Space Header

0x00C

BIST Header Type Primary Latency Timer Cache

Line Size

Type 1 Configuration Space Header

0x010

Base Address 0

Base Address Registers (Offset 10h/14h)

0x014

Base Address 1

Base Address Registers (Offset 10h/14h)

0x018

Secondary Latency Timer Subordinate Bus

Number Secondary Bus Number Primary Bus

Number

Secondary Latency Timer (Offset 1Bh)/Type 1

Configuration Space Header/ /Primary Bus Number

(Offset 18h)

0x01C

Secondary Status I/O Limit I/O Base

Secondary Status Register (Offset 1Eh) / Type 1

Configuration Space Header

0x020

Memory Limit Memory Base

Type 1 Configuration Space Header

0x024

Prefetchable Memory Limit Prefetchable Memory

Base

Prefetchable Memory Base/Limit (Offset 24h)

0x028

Prefetchable Base Upper 32 Bits

Type 1 Configuration Space Header

0x02C

Prefetchable Limit Upper 32 Bits

Type 1 Configuration Space Header

0x030

I/O Limit Upper 16 Bits I/O Base Upper 16 Bits

Type 1 Configuration Space Header

0x034

Reserved Capabilities PTR

Type 1 Configuration Space Header

0x038

Expansion ROM Base Address

Type 1 Configuration Space Header

0x03C

Bridge Control Interrupt Pin Interrupt Line

Bridge Control Register (Offset 3Eh)

Table 6-4.

MSI Capability Structure, Rev2.1 Spec: MSI Capability Structures

0x050

Message Control Next Cap Ptr Capability ID

MSI and MSI-X Capability Structures

0x054

Message Address

MSI and MSI-X Capability Structures

0x058

Message Upper Address

MSI and MSI-X Capability Structures

0x05C

Reserved Message Data

MSI and MSI-X Capability Structures

Table 6-5.

MSI-X Capability Structure, Rev2.1 Spec: MSI-X Capability Structures

0x68

Message Control Next Cap Ptr Capability ID

MSI and MSI-X Capability Structures

0x6C

MSI-X Table Offset BIR

MSI and MSI-X Capability Structures

0x70

Pending Bit Array (PBA) Offset BIR

MSI and MSI-X Capability Structures

Table 6-6.

Power Management Capability Structure, Rev2.1 Spec

0x078

Capabilities Register Next Cap PTR Cap ID

PCI Power Management Capability Structure

0x07C

Data PM Control/Status Bridge Extensions Power

Management Status & Control

PCI Power Management Capability Structure

Table 6-7

PCI Express AER Capability Structure, Rev2.1 Spec: Advanced Error Reporting Capability

0x800

PCI Express Enhanced Capability Header

Advanced Error Reporting Enhanced Capability

Header

0x804

Uncorrectable Error Status Register

Uncorrectable Error Status Register

0x808

Uncorrectable Error Mask Register

Uncorrectable Error Mask Register

Table 8–39. Correspondence Configuration Space Registers and PCIe Base Specification Rev. 2.1 (Part 3 of 4)

Byte Address

Hard IP Configuration Space Register

Corresponding Section in PCIe Specification