Msi-x, Msi-x –3 – Altera Arria V Hard IP for PCI Express User Manual

Page 197

Chapter 11: Interrupts

11–3

Interrupts for Endpoints Using the Avalon-ST Application Interface

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

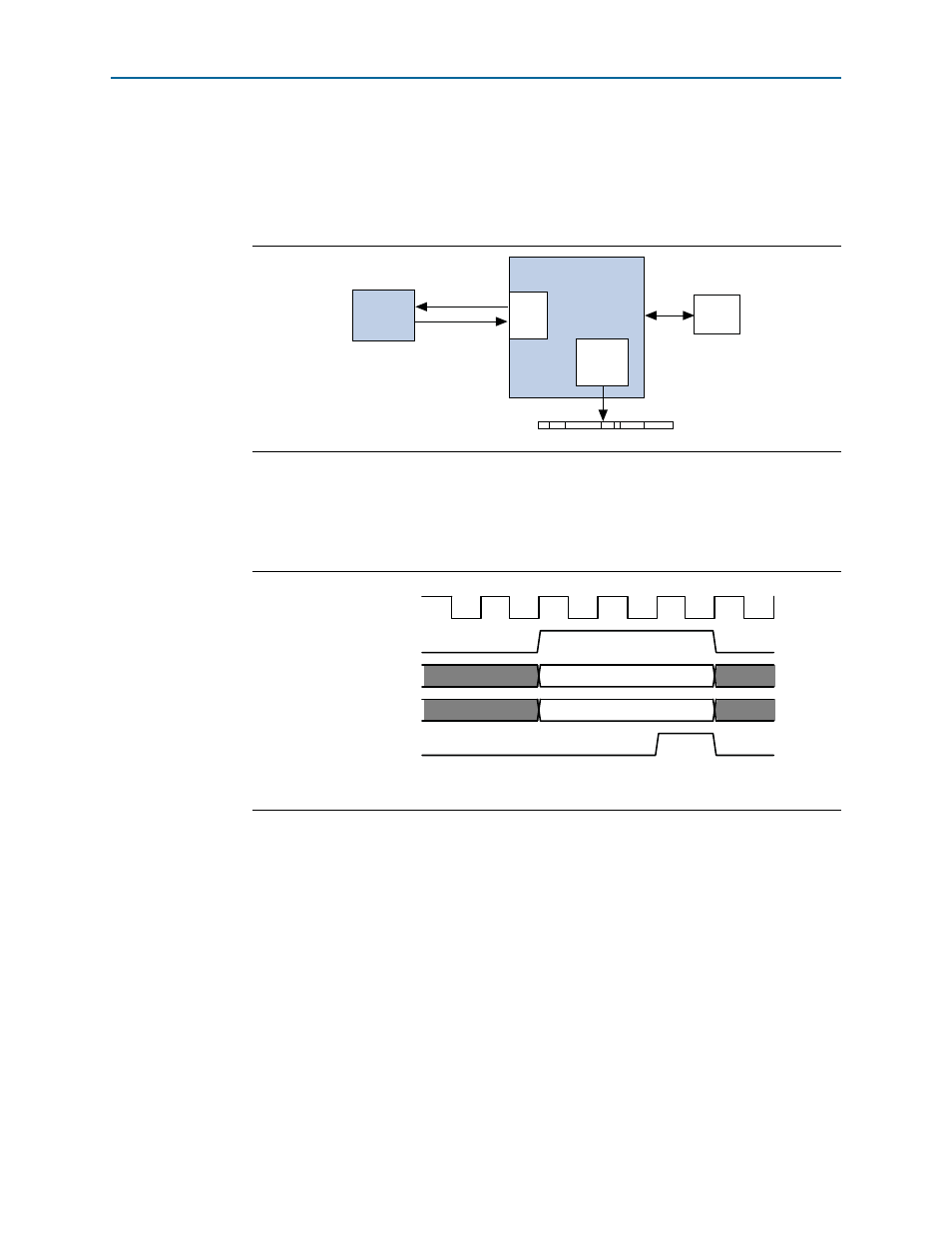

There are 32 possible MSI messages. The number of messages requested by a

particular component does not necessarily correspond to the number of messages

allocated. For example, in

, the Endpoint requests eight MSIs but is only

allocated two. In this case, you must design the Application Layer to use only two

allocated messages.

illustrates the interactions among MSI interrupt signals for the Root Port

. The minimum latency possible between

app_msi_req

and

app_msi_ack

is one clock cycle.

MSI-X

You can enable MSI-X interrupts by turning on Implement MSI-X on the MSI-X tab

under the PCI Express/PCI Capabilities heading using the parameter editor. If you

turn on the Implement MSI-X option, you should implement the MSI-X table

structures at the memory space pointed to by the BARs as part of your Application

Layer.

MSI-X TLPs are generated by the Application Layer and sent through the TX

interface. They are single dword memory writes so that

Last DW Byte Enable

in the

TLP header must be set to 4b’0000. MSI-X TLPs should be sent only when enabled by

the MSI-X enable and the function mask bits in the message control for MSI-X

Configuration register. These bits are available on the

tl_cfg_ctl

output bus.

Figure 11–3. MSI Request Example

Figure 11–4. MSI Interrupt Signals Waveform

Note to

(1)

app_msi_req

can extend beyond

app_msi_ack

before deasserting. F

Endpoint

8 Requested

2 Allocated

Root Complex

CPU

Interrupt Register

Root

Port

Interrupt

Block

coreclkout

app_msi_req

app_msi_tc[2:0]

app_msi_num[4:0]

app_msi_ack

1

2

3

5

6

4

valid

valid