Avalon-mm to pci express interrupt registers, Avalon-mm to pci express interrupt registers –12 – Altera Arria V Hard IP for PCI Express User Manual

Page 166

8–12

Chapter 8: Register Descriptions

PCI Express Avalon-MM Bridge Control Register Access Content

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

Avalon-MM to PCI Express Interrupt Registers

The registers in this section contain status of various signals in the PCI Express

Avalon-MM bridge logic and allow PCI Express interrupts to be asserted when

enabled. Only Root Complexes should access these registers; however, hardware does

not prevent other Avalon-MM masters from accessing them.

Table 8–25

shows the status of all conditions that can cause a PCI Express interrupt to

be asserted.

A PCI Express interrupt can be asserted for any of the conditions registered in the

Avalon-MM to

PCI Express

Interrupt Status

register by setting the corresponding

bits in the Avalon-MM-to-PCI Express

Interrupt Enable

register (

Table 8–26

). Either

MSI or legacy interrupts can be generated as explained in the section

or Legacy Interrupts” on page 11–7

.

0x3A00-0x3A1F

Avalon-MM-to-PCI Express Mailbox Registers 0x3A00–0x3A1F

0x3B00-0x3B1F

PCI Express-to-Avalon-MM Mailbox Registers 0x3B00–0x3B1F

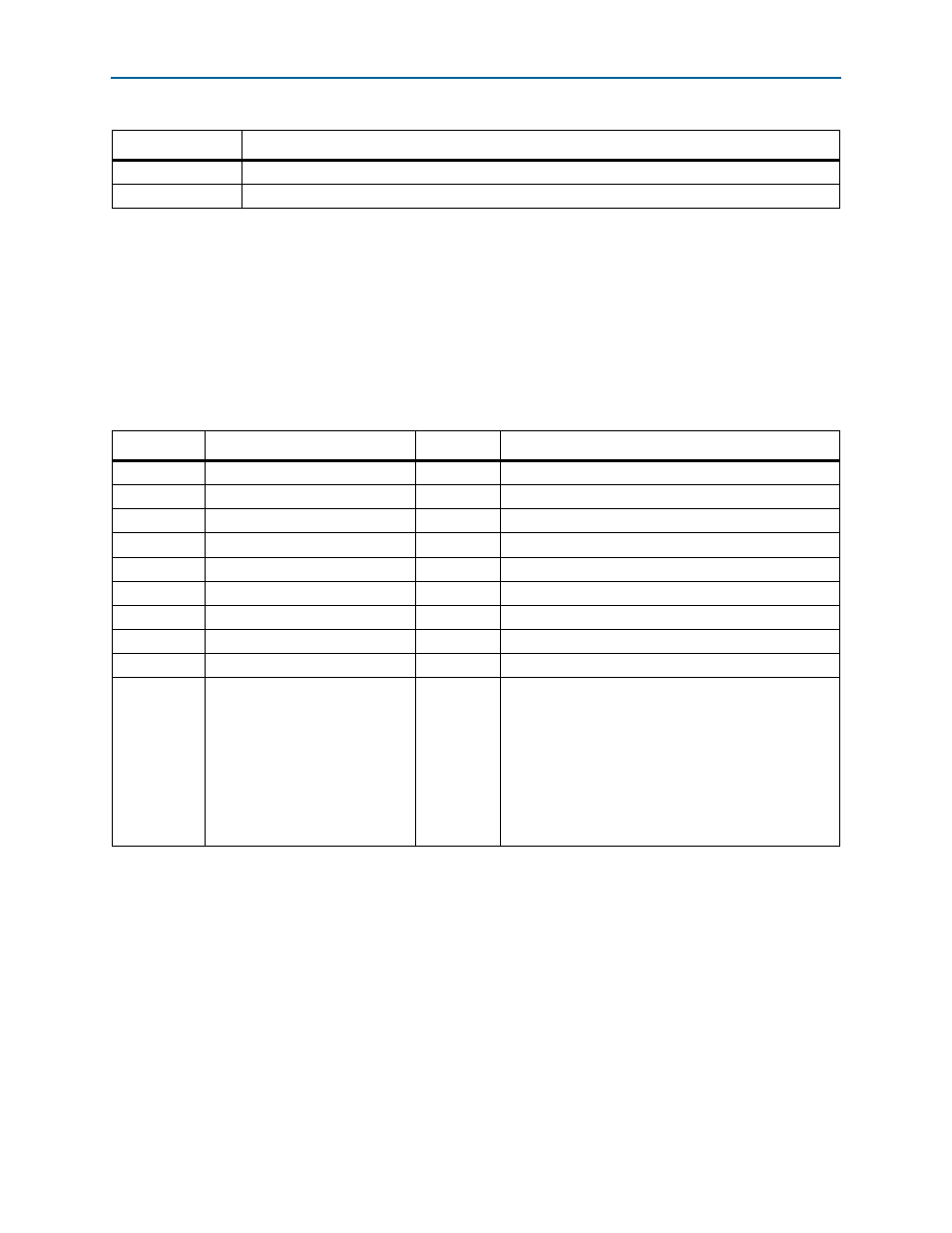

Table 8–24. PCI Express Avalon-MM Bridge Register Map (Part 2 of 2)

Address Range

Register

Table 8–25. Avalon-MM to PCI Express Interrupt Status Register

0x0040

Bit

Name

Access Description

31:24

Reserved

—

—

23

A2P_MAILBOX_INT7

RW1C

1 when the A2P_MAILBOX7 is written to

22

A2P_MAILBOX_INT6

RW1C

1 when the A2P_MAILBOX6 is written to

21

A2P_MAILBOX_INT5

RW1C

1 when the A2P_MAILBOX5 is written to

20

A2P_MAILBOX_INT4

RW1C

1 when the A2P_MAILBOX4 is written to

19

A2P_MAILBOX_INT3

RW1C

1 when the A2P_MAILBOX3 is written to

18

A2P_MAILBOX_INT2

RW1C

1 when the A2P_MAILBOX2 is written to

17

A2P_MAILBOX_INT1

RW1C

1 when the A2P_MAILBOX1 is written to

16

A2P_MAILBOX_INT0

RW1C

1 when the A2P_MAILBOX0 is written to

[15:0]

AVL_IRQ_ASSERTED[15:0]

RO

Current value of the Avalon-MM interrupt (IRQ) input

ports to the Avalon-MM RX master port:

■

0 – Avalon-MM IRQ is not being signaled.

■

1 – Avalon-MM IRQ is being signaled.

A Qsys-generated IP Compiler for PCI Express has as

many as 16 distinct IRQ input ports. Each

AVL_IRQ_ASSERTED[]

bit reflects the value on the

corresponding IRQ input port.