Ecrc forwarding, Clock signals, Ecrc forwarding –23 – Altera Arria V Hard IP for PCI Express User Manual

Page 121: Clock signals –23, Clock

Chapter 7: IP Core Interfaces

7–23

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

To ensure proper operation when sending Configuration Type 0 transactions in Root

Port mode, the application should wait for the Configuration Type 0 transaction to be

transferred to the Hard IP for PCI Express Configuration Space before issuing another

packet on the Avalon-ST TX port. You can do this by waiting for the core to respond

with a completion on the Avalon-ST RX port before issuing the next Configuration

Type 0 transaction.

ECRC Forwarding

On the Avalon-ST interface, the ECRC field follows the same alignment rules as

payload data. For packets with payload, the ECRC is appended to the data as an extra

dword of payload. For packets without payload, the ECRC field follows the address

alignment as if it were a one dword payload. Depending on the address alignment,

through

Figure 7–13 on page 7–13

illustrate the position of the

ECRC data for RX data.

through

Figure 7–25 on page 7–21

illustrate the position of ECRC data for TX data. For packets with no payload data, the

ECRC corresponds to the position of Data0 in these figures.

Clock Signals

describes the clock signals that comprise the clock interface.

Refer to

for more information about the clock interface.

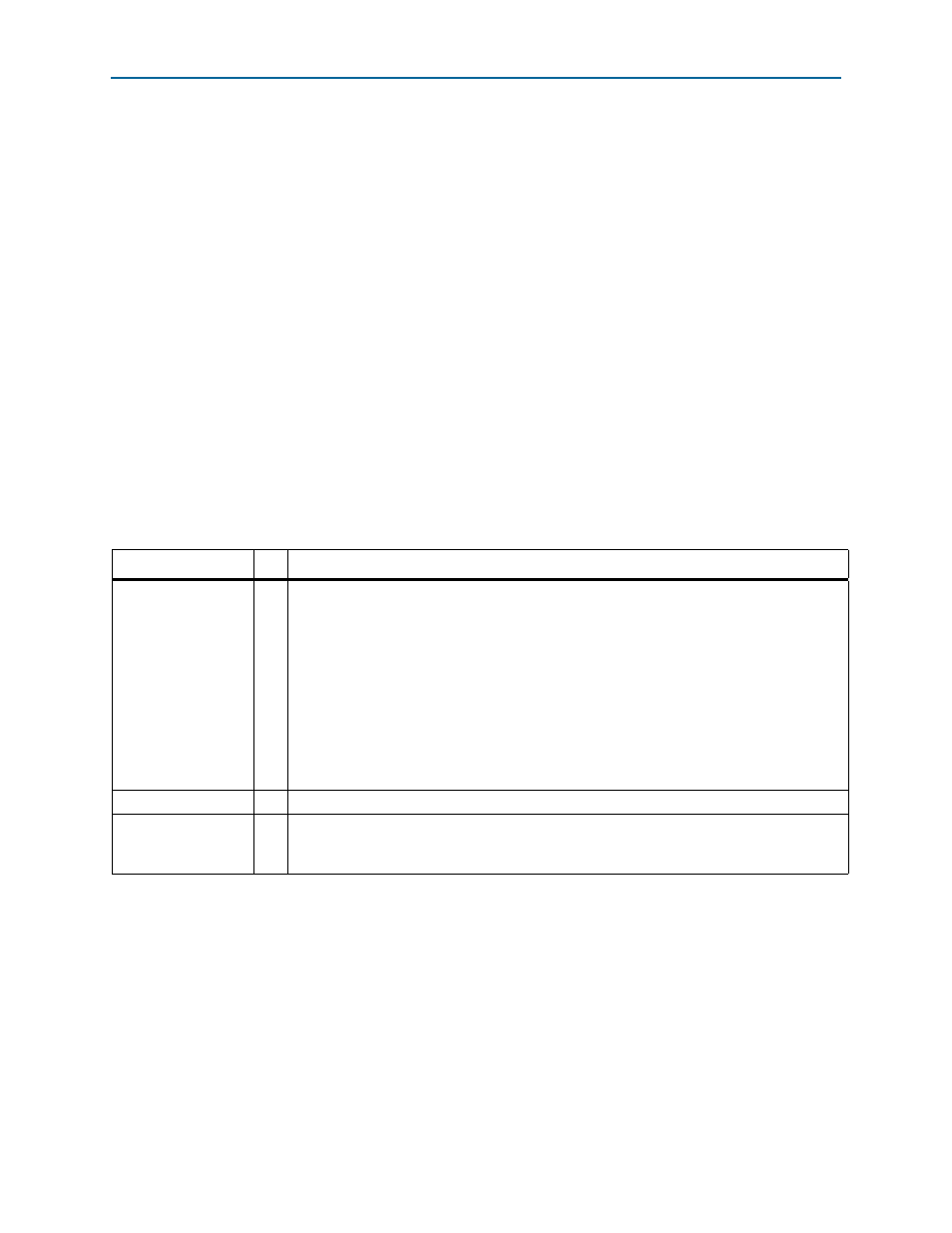

Table 7–5. Clock Signals Hard IP Implementation

Signal

I/O

Description

refclk

I

Reference clock for the Arria V Hard IP for PCI Express. It must have the frequency specified

under the System Settings heading in the parameter editor.

If your design meets the following criteria:

■

It enables CvP

■

Includes an additional transceiver PHY connected to the same Transceiver Reconfiguration

Controller

then you must connect

refclk

to the

mgmt_clk_clk

signal of the Transceiver

Reconfiguration Controller and the additional transceiver PHY. In addition, if your design

includes more than one Transceiver Reconfiguration Controller on the same side of the FPGA,

they all must share the

mgmt_clk_clk

signal.

pld_clk

I

Clocks the Application Layer. You must drive this clock with

coreclkout_hip

.

coreclkout_hip

O

This is a fixed frequency clock used by the Data Link and Transaction Layers. To meet PCI

Express link bandwidth constraints, this clock has minimum frequency requirements as listed

in

.

Note to

(1)

illustrates these clock signals.