Altera Arria V Hard IP for PCI Express User Manual

Page 177

Chapter 8: Register Descriptions

8–23

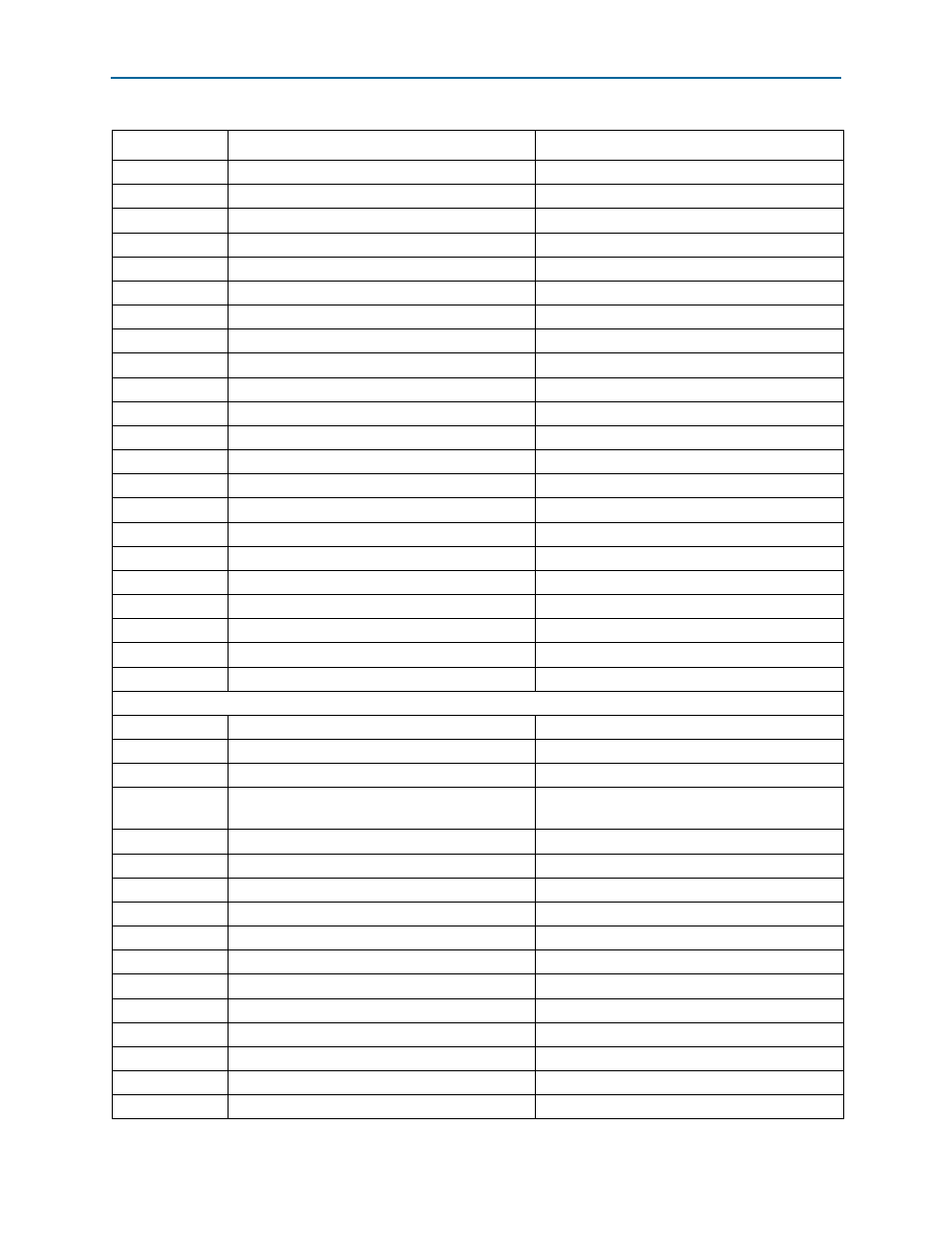

Correspondence between Configuration Space Registers and the PCIe Spec 2.1

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

0x050:0x05C

MSI Capability Structure

MSI and MSI-X Capability Structures

0x068:0x070

MSI Capability Structure

MSI and MSI-X Capability Structures

0x070:0x074 Reserved

0x078:0x07C

Power Management Capability Structure

PCI Power Management Capability Structure

0x080:0x0B8

PCI Express Capability Structure

PCI Express Capability Structure

0x080:0x0B8

PCI Express Capability Structure

PCI Express Capability Structure

0x0B8:0x0FC Reserved

0x094:0x0FF Root

Port

0x100:0x16C

Virtual Channel Capability Structure (Reserved)

Virtual Channel Capability

0x170:0x17C Reserved

0x180:0x1FC

Virtual channel arbitration table (Reserved)

VC Arbitration Table

0x200:0x23C

Port VC0 arbitration table (Reserved)

Port Arbitration Table

0x240:0x27C

Port VC1 arbitration table (Reserved)

Port Arbitration Table

0x280:0x2BC

Port VC2 arbitration table (Reserved)

Port Arbitration Table

0x2C0:0x2FC

Port VC3 arbitration table (Reserved)

Port Arbitration Table

0x300:0x33C

Port VC4 arbitration table (Reserved)

Port Arbitration Table

0x340:0x37C

Port VC5 arbitration table (Reserved)

Port Arbitration Table

0x380:0x3BC

Port VC6 arbitration table (Reserved)

Port Arbitration Table

0x3C0:0x3FC

Port VC7 arbitration table (Reserved)

Port Arbitration Table

0x400:0x7FC

Reserved

PCIe spec corresponding section name

0x800:0x834

Advanced Error Reporting AER (optional)

Advanced Error Reporting Capability

0x838:0xFFF Reserved

Table 6-2.

PCI Type 0 Configuration Space Header (Endpoints), Rev2.1

0x000

Device ID Vendor ID

Type 0 Configuration Space Header

0x004

Status Command

Type 0 Configuration Space Header

0x008

Class Code Revision ID

Type 0 Configuration Space Header

0x00C

BIST Header Type Master Latency Time Cache Line

Size

Type 0 Configuration Space Header

0x010

Base Address 0

Base Address Registers (Offset 10h - 24h)

0x014

Base Address 1

Base Address Registers (Offset 10h - 24h)

0x018

Base Address 2

Base Address Registers (Offset 10h - 24h)

0x01C

Base Address 3

Base Address Registers (Offset 10h - 24h)

0x020

Base Address 4

Base Address Registers (Offset 10h - 24h)

0x024

Base Address 5

Base Address Registers (Offset 10h - 24h)

0x028

Reserved

Type 0 Configuration Space Header

0x02C

Subsystem Device ID Subsystem Vendor ID

Type 0 Configuration Space Header

0x030

Expansion ROM base address

Type 0 Configuration Space Header

0x034

Reserved Capabilities PTR

Type 0 Configuration Space Header

0x038

Reserved

Type 0 Configuration Space Header

0x03C

Max_Lat Min_Gnt Interrupt Pin Interrupt Line

Type 0 Configuration Space Header

Table 8–39. Correspondence Configuration Space Registers and PCIe Base Specification Rev. 2.1 (Part 2 of 4)

Byte Address

Hard IP Configuration Space Register

Corresponding Section in PCIe Specification