Arria v hard ip for pci express, Arria v hard ip for pci express –3 – Altera Arria V Hard IP for PCI Express User Manual

Page 101

Chapter 7: IP Core Interfaces

7–3

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

Arria V Hard IP for PCI Express

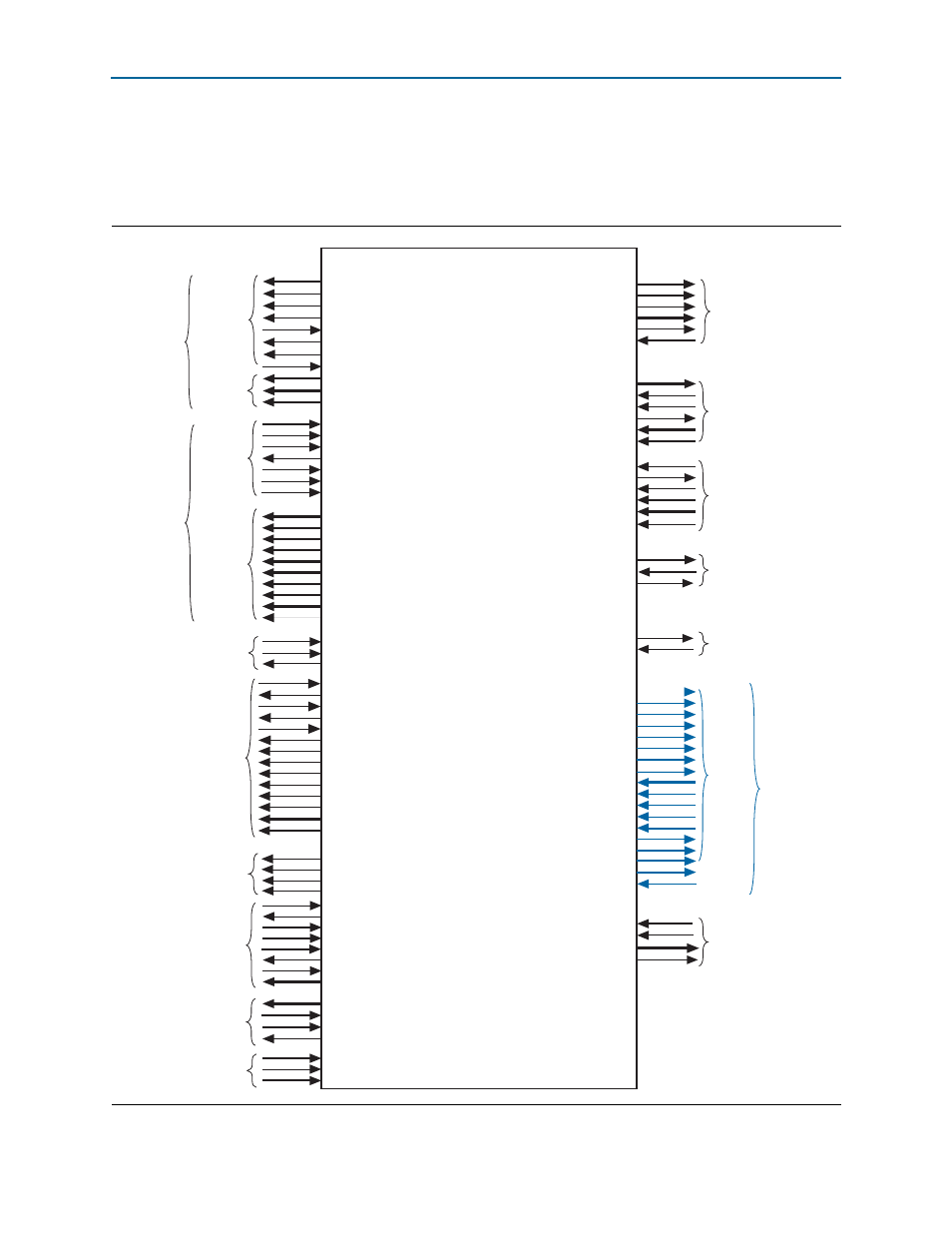

Figure 7–2

illustrates the top-level signals in Arria V Hard IP for PCI Express IP core.

Signal names that include also exist for functions 1 to 7.

Figure 7–2. Signals in the Arria V Hard IP for PCI Express with Avalon-ST Interface

rx_st_data[63:0], [127:0]

rx_st_sop

rx_st_eop

rx_st_empty

rx_st_ready

rx_st_valid

rx_st_err

rx_st_mask

rx_st_bar[7:0]

rx_st_be[7:0]

rx_bar_dec_func_num[2:0]

Arria V Hard IP for PCI Express, Avalon-ST Interface

Test

Interface

RX Port

tx_st_data[63:0], [127:0]

tx_st_sop

tx_st_eop

tx_st_ready

tx_st_valid

tx_st_empty

tx_st_err

tx_cred_datafccp[11:0]

tx_cred_datafcnp[11:0]

tx_cred_datafcp[11:0]

tx_cred_fchipons[5:0]

tx_cred_fcinfinite[5:0]

tx_cred_hdrfccp[7:0]

tx_cred_hdrfcnp[7:0]

tx_cred_hdrfcp[7:0]

ko_cpl_spc_header[7:0]

ko_cpl_spc_data[11:0]

Clocks

Power

Managementt

TX Port

Transaction Layer

Configuration

ECC Error

Completion

Interface

LMI

txdata0[7:0]

txdatak0

txdetectrx0

txelecidle0

txcompl0

rxpolarity0

powerdown0[1:0]

tx_deemph

rxdata0[7:0]

rxdatak0

rxvalid0

phystatus0

eidleinferset0[[2:0]

rxelecidle0

rxstatus0[2:0]

sim_ltssmstate[4:0]

sim_pipe_rate[1:0]

sim_pipe_pclk_in

8-bit

PIPE

test_in[31:0]

simu_mode_pipe

lane_act[3:0]

testin_zero

tl_cfg_add[6:0]

tl_cfg_ctl[31:0]

tl_cfg_ctl_wr

tl_cfg_sts[122:0]

tl_cfg_sts_wr

tl_hpg_ctrler[4:0]

lmi_dout[31:0]

lmi_rden

lmi_wren

lmi_ack

lmi_addr[14:0]

lmi_din[31:0]

reconfig_fromxcvr[(

70-1):0]

reconfig_toxcvr[(

46-1):0]

busy_xcvr_reconfig

Transceiver

Reconfiguration

for internal PHY

x number of lanes

tx_out0

rx_in0

Serial IF to PIPE

Avalon-ST

Avalon-ST

Component

Specific

Component

Specific

TX

Credit

derr_cor_ext_rcv0

derr_cor_ext_rcv1

derr_rpl

derr_cor_ext_rpl0

Interrupts

(Root Port)

int_status[3:0]

aer_msi_num[4:0]

pex_msi_num[4:0]

serr_out

cpl_err[6:0]

cpl_pending

cpl_err_func[2:0]

Interrupt

(Endpoint)

tl_app_msi_req

tl_app_msi_ack

tl_app_msi_tc[2:0]

tl_app_msi_num[4:0]

tl_app_msi_func[2:0]

tl_app_int

_sts

tl_app_int

_ack

tl_app_int

_funcnum[2:0]

pme_to_cr

pme_to_sr

pm_event

pm_event_func[2:0]

pm_data[9:0]

pm_auxpwr

refclk

pld_clk

coreclkout_hip

npor

reset_status

pin_perstn

sedes_pll_locked

pld_core_ready

pld_clk_inuse

dlup

dlup_exit

ev128ns

ev1us

hotrst_exit

l2_exit

dl_current_speed[1:0]

dl_ltssm[4:0]

Reset &

Lock Status

PIPE

Interface

for Simulat

and Hardwa

Debug Usi

dl_ltssm[4

in SignalTa