Altera Arria V Hard IP for PCI Express User Manual

Page 142

7–44

Chapter 7: IP Core Interfaces

Avalon-MM Hard IP for PCI Express

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

f

Variations with Avalon-MM interface implement the Avalon-MM protocol described

in the

specification for information about

the Avalon-MM protocol, including timing diagrams.

32-Bit Non-Bursting Avalon-MM Control Register Access (CRA) Slave

Signals

The optional CRA port for the full-featured IP core allows upstream PCI Express

devices and external Avalon-MM masters to access internal control and status

registers.

Table 7–21

describes the CRA slave signals.

Clock

v

v

Reset and Status

v

v

Physical and Test

Transceiver Control

v

v

“Transceiver Reconfiguration” on page 7–47

Serial

v

v

“Serial Interface Signals” on page 7–47

Pipe

v

v

“PIPE Interface Signals” on page 7–51

Test

v

v

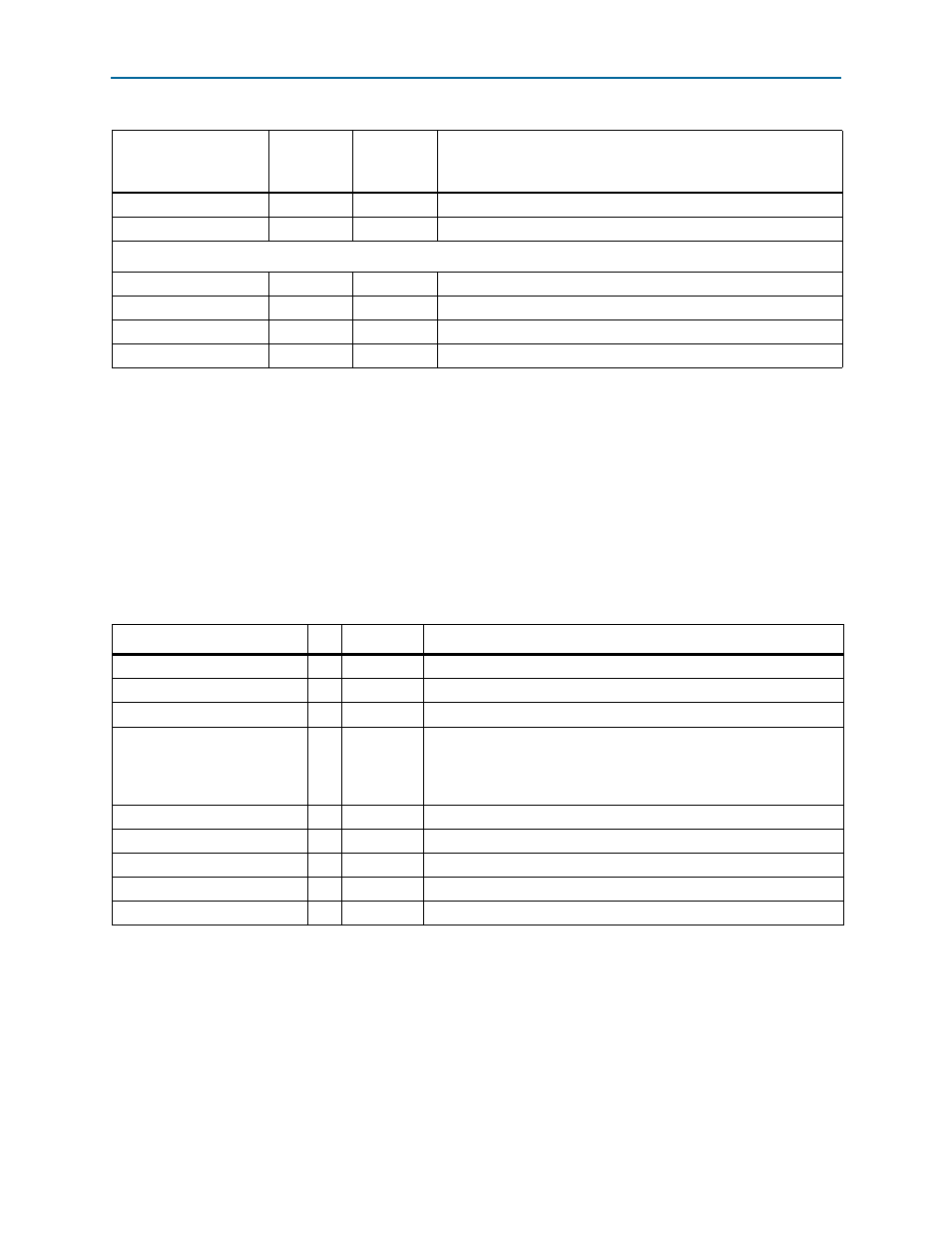

Table 7–20. Signal Groups in the Avalon-MM Arria V Hard IP for PCI Express Variants (Part 2 of 2)

Signal Group

Full

Featured

Completer

Only Single

DWord

Description

Table 7–21. Avalon-MM CRA Slave Interface Signals

Signal Name

I/O

Type

Description

CraIrq_o

O

Irq

Interrupt request. A port request for an Avalon-MM interrupt.

CraReadData_o[31:0]

O

Readdata

Read data lines.

CraWaitRequest_o

O

Waitrequest Wait request to hold off more requests.

CraAddress_i[11:0]

I

Address

An address space of 16,384 bytes is allocated for the control registers.

Avalon-MM slave addresses provide address resolution down to the

width of the slave data bus. Because all addresses are byte addresses,

this address logically goes down to bit 2. Bits 1 and 0 are 0.

CraByteEnable_i[3:0]

I

Byteenable

Byte enable.

CraChipSelect_i

I

Chipselect

Chip select signal to this slave.

CraRead

I

Read

Read enable.

CraWrite_i

I

Write

Write request.

CraWriteData_i[31:0]

I

Writedata

Write data.