Figure 7–17 – Altera Arria V Hard IP for PCI Express User Manual

Page 116

7–18

Chapter 7: IP Core Interfaces

Arria V Hard IP for PCI Express

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

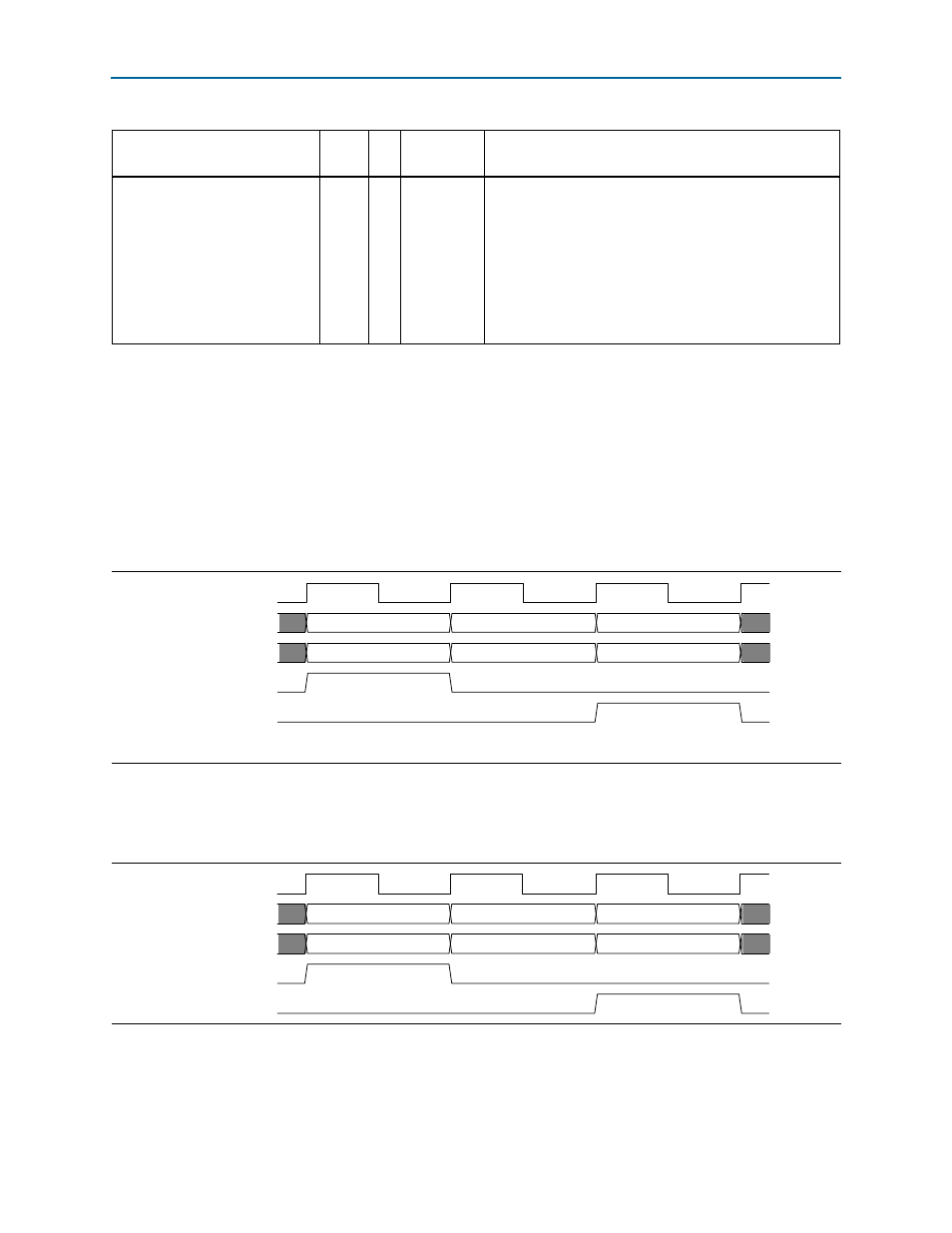

Data Alignment and Timing for the 64-Bit Avalon-ST TX Interface

illustrates the mapping between Avalon-ST TX packets and PCI Express

TLPs for 3 dword header TLPs with non-qword aligned addresses with a 64-bit bus.

(

Figure 7–3 on page 7–5

illustrates the storage of non-qword aligned data.)

Non-qword aligned addresses occur when address[2] is set. When address[2] is set,

tx_st_data[63:32]

contains

Data0

and

tx_st_data[31:0]

contains dword

header2

.

illustrates the mapping between Avalon-ST TX packets and PCI Express

TLPs for a four dword header with qword aligned addresses with a 64-bit bus.

ko_cpl_spc_data

12

O

component

specific

ko_cpl_spc_data

is a static signal that reflects the total

number of 16 byte completion data units that can be stored

in the completion RX buffer. The total read data from all

outstanding MRd requests must be less than this value to

prevent RX FIFO overflow. The Application Layer can use

this signal to build circuitry to prevent RX buffer overflow

for completion data. Endpoints must advertise infinite

space for completion data; however, RX buffer space is

finite.

Note to

(1) To be Avalon-ST compliant, your application have a

readyLatency

of 1 or 2 cycles.

Table 7–4. 64- or 128-Bit Avalon-ST TX Datapath (Part 4 of 4)

Signal

Width

Dir

Avalon-ST

Type

Description

Figure 7–17. 64-Bit Avalon-ST tx_st_data Cycle Definition for 3-Dword Header TLP with Non-Qword Aligned Address

coreclkout

tx_st_data[63:32]

tx_st_data[31:0]

tx_st_sop

tx_st_eop

Header1

Data0

Data2

Header0

Header2

Data1

Figure 7–18. 64-Bit Avalon-ST tx_st_data Cycle Definition for 4-Dword TLP with Qword Aligned Address

coreclkout

tx_st_data[63:32]

tx_st_data[31:0]

tx_st_sop

tx_st_eop

Header1

Header3

Data1

Header0

Header2

Data0