Pci express/pci capabilities for func Page 62

Page 62

4–10

Chapter 4: Parameter Settings for the Arria V Hard IP for PCI Express

Port Functions

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

PCI Express/PCI Capabilities for Func

The following sections describe the PCI Express and PCI Capabilities for each

function.

Device

describes the Device Capabilities register parameters.

Link

Table 4–12

describes the Link Capabilities register parameters.

MSI

Table 4–12

describes the MSI Capabilities register parameters.

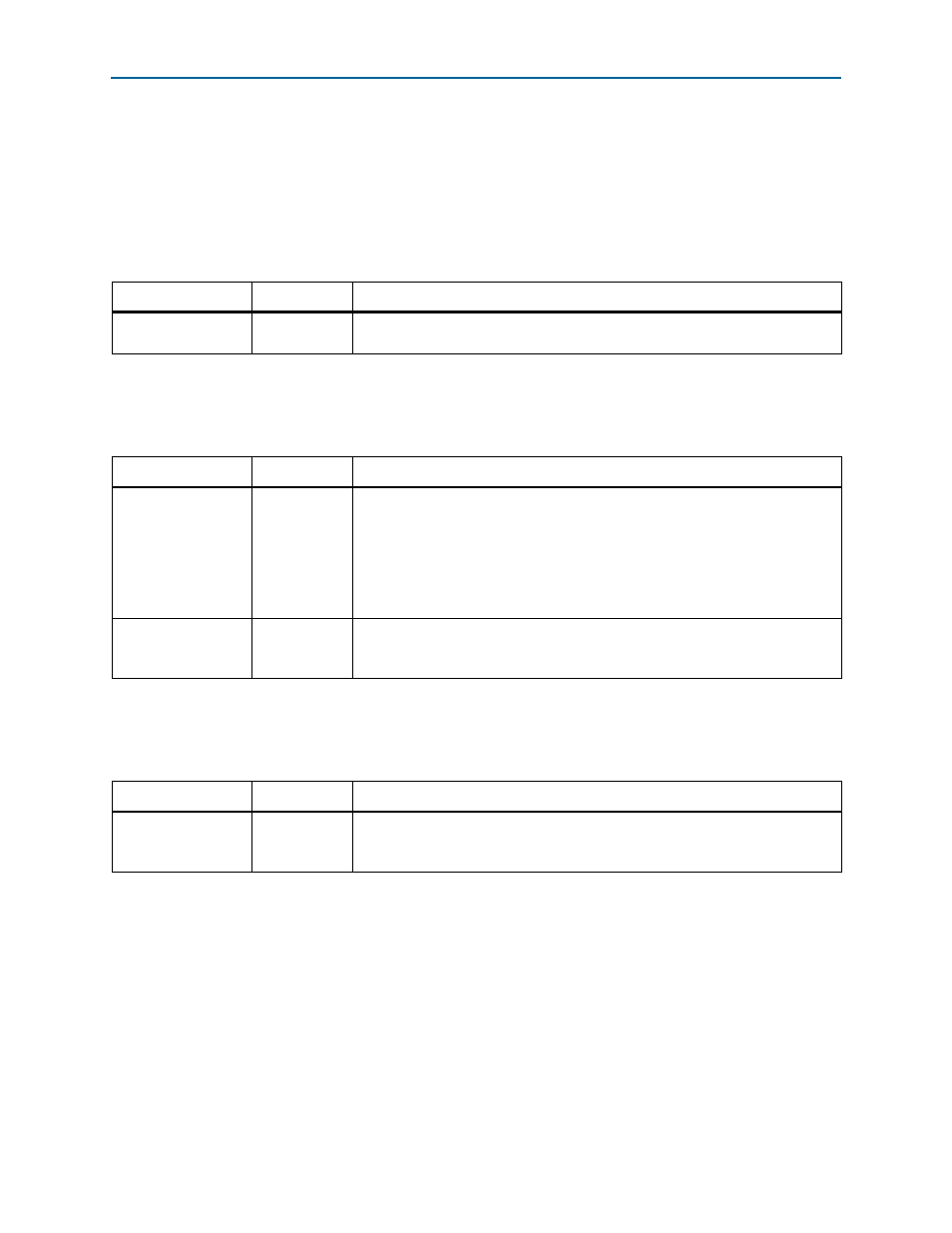

Table 4–10. Function Level Reset

Parameter

Value

Description

Function level reset

On/Off

Turn On this option to set the Function Level Reset Capability bit in the

Device

Capabilities

register. This parameter applies to Endpoints only.

Table 4–11. Link

Parameter

Value

Description

Data link layer active

reporting

On/Off

Turn On this parameter for a downstream port, if the component supports the

optional capability of reporting the DL_Active state of the Data Link Control and

Management State Machine. For a hot-plug capable downstream port (as

indicated by the

Hot-Plug Capable

field of the

Slot

Capabilities

register),

this parameter must be turned On. For upstream ports and components that do

not support this optional capability, turn Off this option. This parameter is only

supported in Root Port mode.

Surprise down

reporting

On/Off

When this option is On, a downstream port supports the optional capability of

detecting and reporting the surprise down error condition. This parameter is only

supported in Root Port mode.

Table 4–12. MSI and MSI-X Capabilities –

Parameter

Value

Description

MSI messages

requested

1, 2, 4,

8, 16

Specifies the number of messages the Application Layer can request. Sets the

value of the

Multiple Message Capable

field of the

Message Control

register, 0x050[31:16].