Altera Arria V Hard IP for PCI Express User Manual

Page 273

Chapter 18: Debugging

18–3

Link Training

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

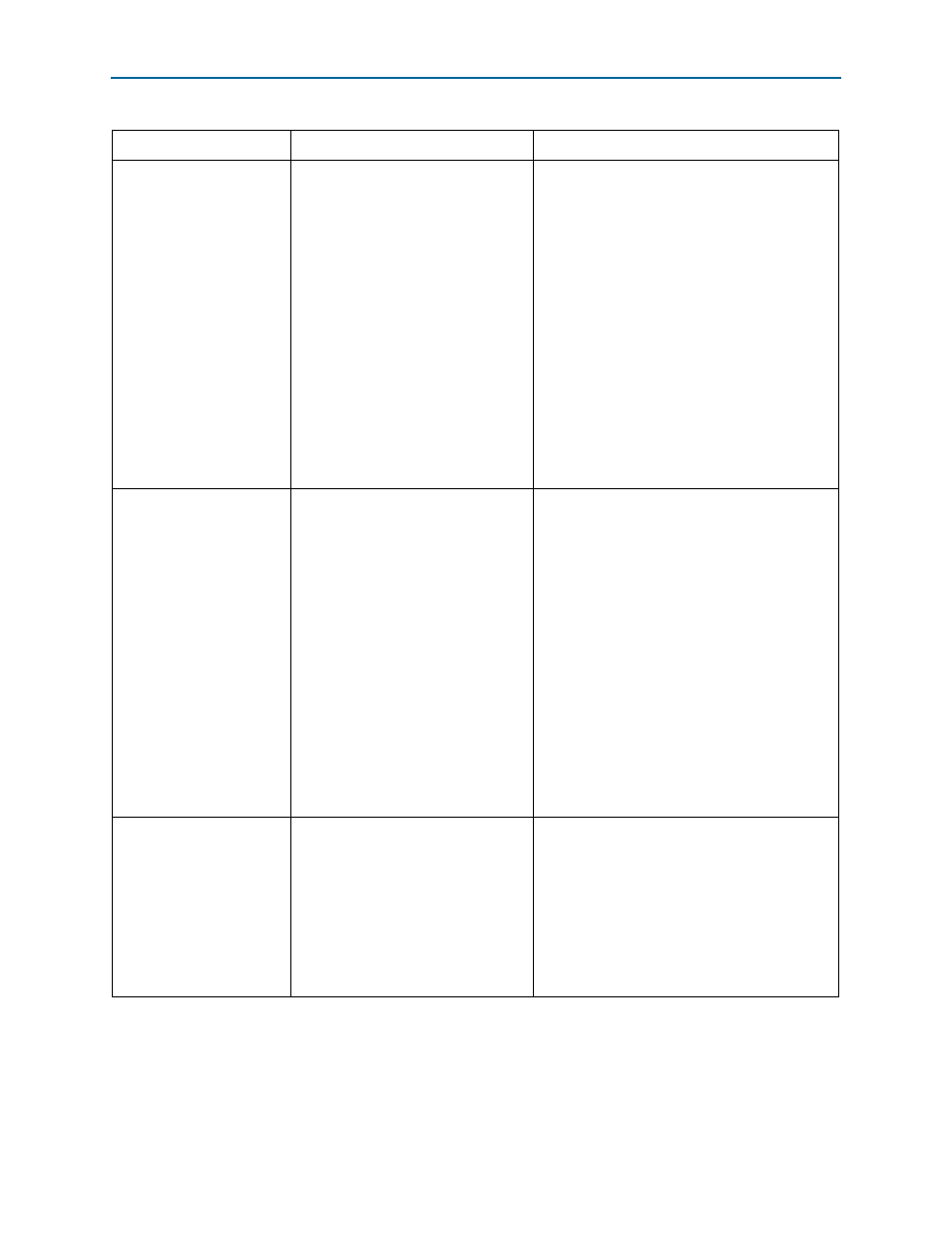

Link fails with the LTSSM

toggling between:

Detect.Quiet (0),

Detect.Active (1), and

Polling.Active (2),

or:

Detect.Quiet (0),

Detect.Active (1), and

Polling.Configuration (4)

On the PIPE interface extracted from

the

test_out

bus, confirm that the

Hard IP for PCI Express IP Core is

transmitting valid TS1 in the

Polling.Active(2) state or TS1 and TS2

in the Polling.Configuration (4) state on

txdata0

. The Root Port should be

sending either the TS1 Ordered Set or a

compliance pattern as seen on

rxdata0

. These symptoms indicate

that the Root Port did not receive the

valid training Ordered Set from

Endpoint because the Endpoint

transmitted corrupted data on the link.

You can debug this issue using

SignalTap II. Refer to

“PIPE Interface

Signals” on page 18–8

for a list of the

test_out

bus signals.

The following are some of the reasons the

Endpoint might send corrupted data:

■

Signal integrity issues. Measure the TX eye and

check it against the eye opening requirements

in the PCI Express Base Specification, Rev 3.0.

Adjust the transceiver pre-emphasis and

equalization settings to open the eye.

■

Bypass the Transceiver Reconfiguration

Controller IP Core to see if the link comes up at

the expected data rate without this component.

If it does, make sure the connection to

Transceiver Reconfig Controller IP Core is

correct.

Link fails due to unstable

rx_signaldetect

Confirm that

rx_signaldetect

bus of

the active lanes is all 1’s. If all active

lanes are driving all 1’s, the LTSSM

state machine toggles between

Detect.Quiet(0), Detect.Active(1), and

Polling.Active(2) states. You can debug

this issue using SignalTap II. Refer to

“PIPE Interface Signals” on page 18–8

for a list of the

test_out

bus signals.

This issue may be caused by mismatches between

the expected power supply to RX side of the

receiver and the actual voltage supplied to the

FPGA from your boards. Arria V devices require

VCCR/VCCT to be 1.1 V. You must apply the

following command to both P and N pins of each

active channel to override the default setting of

0.85 V.

For example, for Arria V devices running at the

Gen1 data rate the correct pin assignment is:

set_instance_assignment -name

XCVR_VCCR_VCCT_VOLTAGE 1.1_0V –to

“pin”

For Gen2, the correct pin assignment is 1.15 V.

Substitute the pin names from your design for

“pin”

. Refer to the

for

complete characterization data.

Link fails because the

LTSSM state machine enters

Compliance

Confirm that the LTSSM state machine

is in Polling.Compliance(3) using

SignalTap II.

Possible causes include the following:

■

Setting

test_in[6]

=1 forces entry to

Compliance mode when a timeout is reached in

the Polling.Active state.

■

Differential pairs are incorrectly connected to

the pins of the device. For example, the

Endpoint’s TX signals are connected to the RX

pins and the Endpoint’s RX signals are to the TX

pins.

Table 18–1. Link Training Fails to Reach L0 (Part 2 of 3)

Possible Causes

Symptoms and Root Causes

Workarounds and Solutions