System settings, System settings –1 – Altera Arria V Hard IP for PCI Express User Manual

Page 65

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

5. Parameter Settings for the Avalon-MM

Arria V Hard IP for PCI Express

This chapter describes the parameters which you can set using the Qsys design flow

to instantiate an Avalon-MM Arria V Hard IP for PCI Express IP core.

1

In the following tables, hexadecimal addresses in

green

are links to additional

information in the

System Settings

The first group of settings defines the overall system.

describes these

settings.

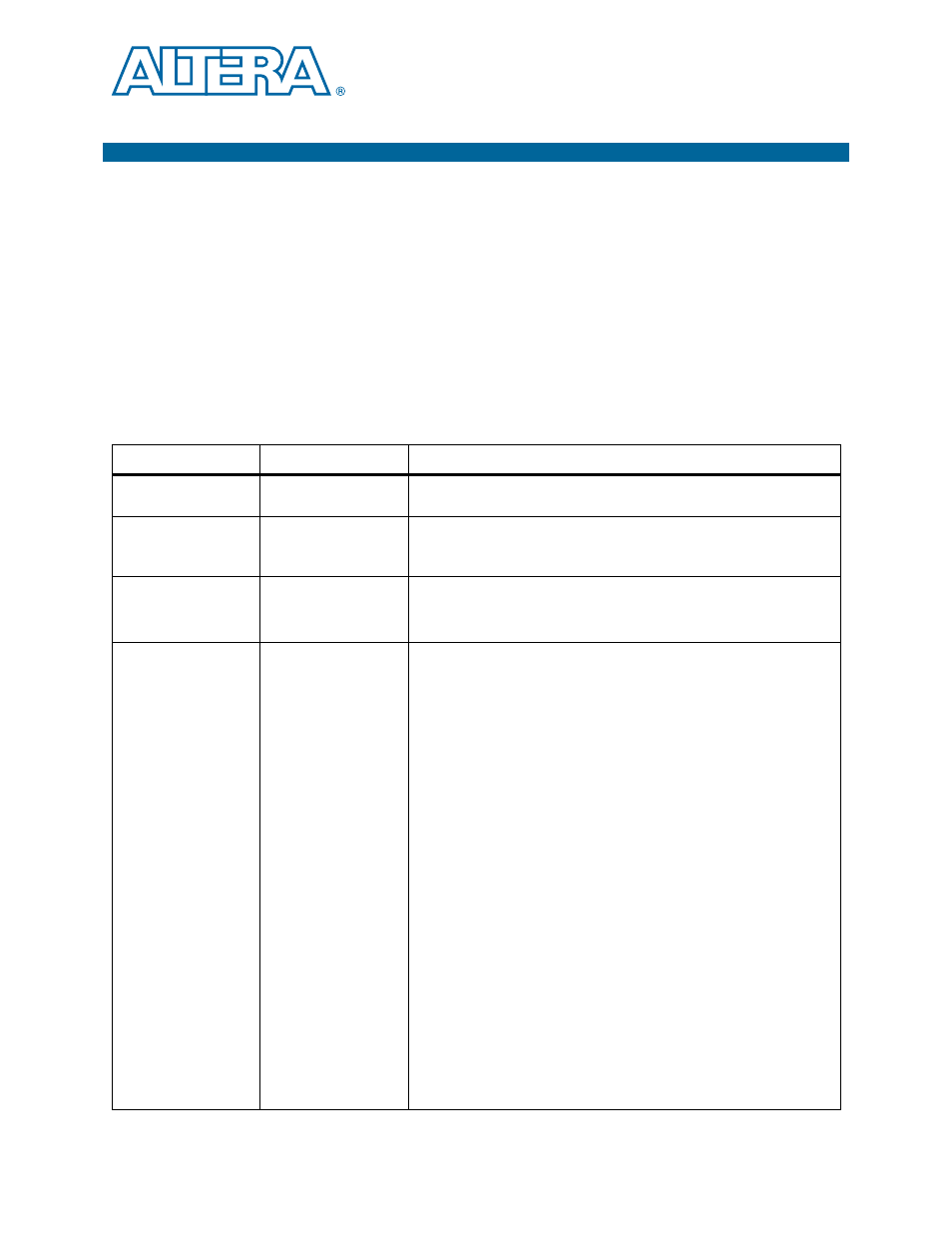

Table 5–1. System Settings for PCI Express (Part 1 of 2)

Parameter

Value

Description

Number of Lanes

×1, ×2, ×4, ×8

Specifies the maximum number of lanes supported. ×2 is currently

supported by down training from ×4.

Lane Rate

Gen1 (2.5 Gbps)

Gen2 (5.0 Gbps)

Specifies the maximum data rate at which the link can operate.

Port type

Native Endpoint

Root Port

Specifies the function of the port.

Native Endpoints store parameters in the Type 0 Configuration Space

which is outlined in

RX Buffer credit

allocation -

performance for

received requests

Minimum

Low

Balanced

High

Maximum

This setting determines the allocation of posted header credits, posted

data credits, non-posted header credits, completion header credits, and

completion data credits in the 6 KByte RX buffer. The 5 settings allow

you to adjust the credit allocation to optimize your system. The credit

allocation for the selected setting displays in the message pane.

, for more information about

optimizing performance. The Flow Control chapter explains how the RX

credit allocation and the Maximum payload size that you choose affect

the allocation of flow control credits. You can set the Maximum payload

size parameter in

Table 5–4 on page 5–4

■

Minimum–This setting configures the minimum PCIe specification

allowed non-posted and posted request credits, leaving most of the

RX Buffer space for received completion header and data. Select this

option for variations where application logic generates many read

requests and only infrequently receives single requests from the PCIe

link.

■

Low– This setting configures a slightly larger amount of RX Buffer

space for non-posted and posted request credits, but still dedicates

most of the space for received completion header and data. Select

this option for variations where application logic generates many read

requests and infrequently receives small bursts of requests from the

PCIe link. This option is recommended for typical endpoint

applications where most of the PCIe traffic is generated by a DMA

engine that is located in the endpoint application layer logic.

December 2013

UG-01110-1.5