Altera Arria V Hard IP for PCI Express User Manual

Page 124

7–26

Chapter 7: IP Core Interfaces

Arria V Hard IP for PCI Express

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

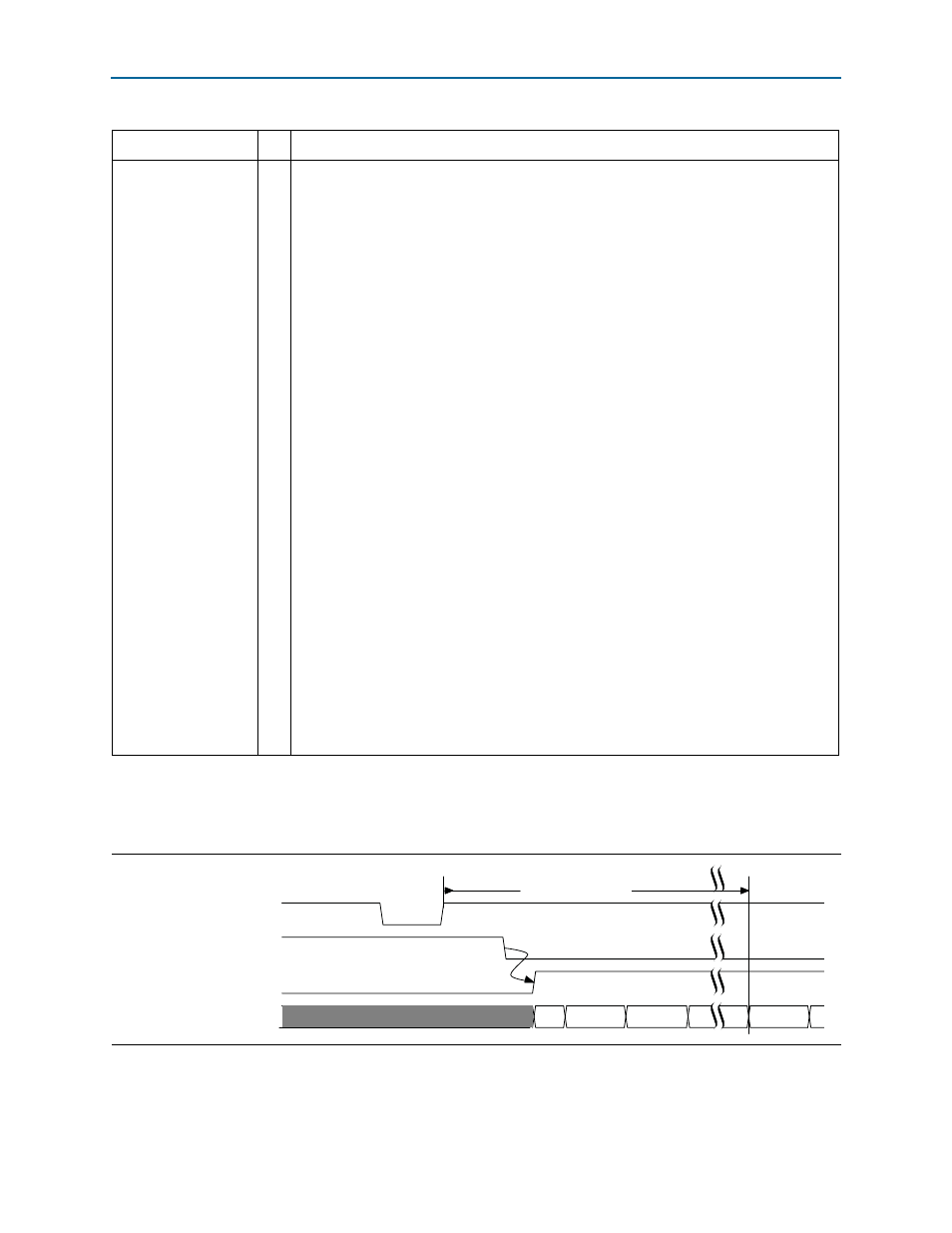

illustrates the timing relationship between

npor

and the LTSSM L0 state.

dl_ltssm[4:0]

O

LTSSM state: The LTSSM state machine encoding defines the following states:

■

00000: detect.quiet

■

00001: detect.active

■

00010: polling.active

■

00011: polling.compliance

■

00100: polling.configuration

■

00101: polling.speed

■

00110: config.linkwidthstart

■

00111: config.linkaccept

■

01000: config.lanenumaccept

■

01001: config.lanenumwait

■

01010: config.complete

■

01011: config.idle

■

01100: recovery.rcvlock

■

01101: recovery.rcvconfig

■

01110: recovery.idle

■

01111: L0

■

10000: disable

■

10001: loopback.entry

■

10010: loopback.active

■

10011: loopback.exit

■

10100: hot.reset

■

10101: L0s

■

10110: L1.entry

■

10111: L1.idle

■

11000: L2.idle

■

11001: L2.transmit.wake

■

11010: recovery.speed

Table 7–6. Reset and Link Training Signals (Part 3 of 3)

Signal

I/O

Description

Figure 7–28. 100 ms Requirement

npor

IO_POF_Load

PCIe_LinkTraining_Enumeration

dl_ltssm[4:0]

detect.

quiet

detect.active polling.active

L0

100 ms (maximum)