Altera Arria V Hard IP for PCI Express User Manual

Page 172

8–18

Chapter 8: Register Descriptions

PCI Express Avalon-MM Bridge Control Register Access Content

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

Figure 8–1

illustrates four dword TLPs with data that is aligned and unaligned to the

qword.

1

For Root Ports, the Avalon-MM bridge does not filter Type 0 Configuration Requests

by device number. Application Layer software should filter out all requests to Avalon-

MM Root Port registers that are not for device 0. Application Layer software should

return an Unsupported Request Completion Status.

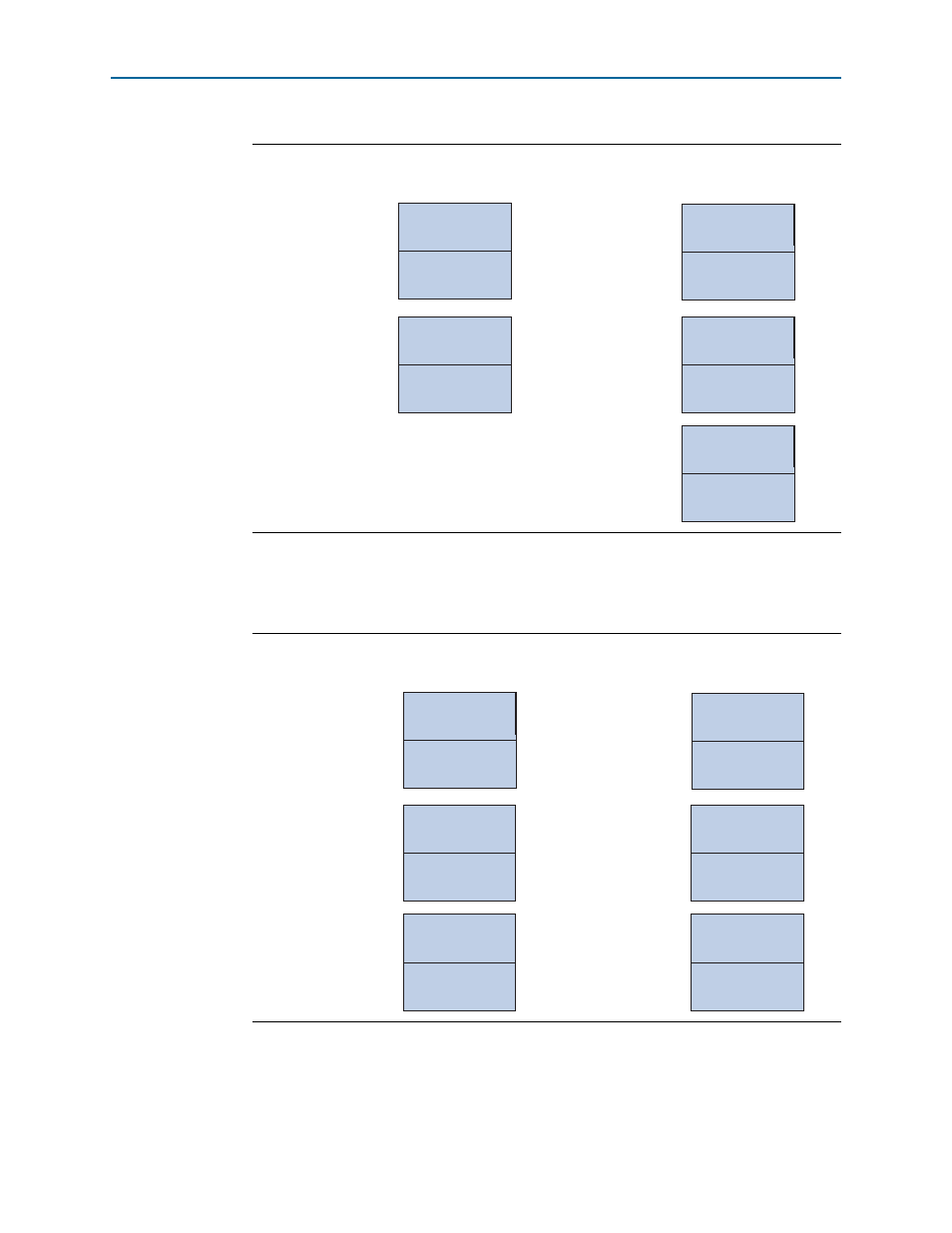

Figure 8–1. Layout of Data with 3 DWord Headers

Figure 8–2. Layout of Data with 4 DWord Headers

Header 1 [63:32]

Cycle 1

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

Data Unaligned to

QWord Boundary

Data Aligned to

QWord Boundary

Cycle 2

Header 0 [31:0]

Data [63:32]

Header 2 [31:0]

Header 1 [63:32]

Cycle 1

Header 0 [31:0]

Cycle 2

Header 2 [31:0]

Unused, but must

be written

Cycle 3

Data [31:0]

Unused, but must

be written

Header 1 [63:32]

Cycle 1

Data Unaligned to

QWord Boundary

Data Aligned to

QWord Boundary

Cycle 2

Header 0 [31:0]

Header 3[63:32]

Header 2 [31:0]

Data [63:32]

Header 1 [63:32]

Header 0 [31:0]

Header 2 [31:0]

Cycle 1

Cycle 2

Cycle 3

Cycle 3

Data [31:0]

Unused, but must

be written

Unused, but must

be written

Header 3[63:32]

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0