Specifying clocks and interrupts, Specifying exported interfaces – Altera Arria V Hard IP for PCI Express User Manual

Page 43

Chapter 3: Getting Started with the Avalon-MM Arria Hard IP for PCI Express

3–9

Specifying Clocks and Interrupts

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

Specifying Clocks and Interrupts

Complete the following steps to connect the clocks and specify interrupts:

1. To connect DUT

coreclkout

to the onchip_memory and dma_0 clock inputs, click

in the Clock column next to the DUT

coreclkout

clock input. Click

onchip_memory.clk1

and dma_0.clk.

2. To connect alt_xcvr_reconfig_0

mgmt_clk_clk

to clk_0

clk

, click in the Clock

column next to the alt_xcvr_reconfig_0

mgmt_clk_clk

clock input. Click clk_0.clk.

3. To specify the interrupt number for DMA interrupt sender,

control_port_slave

,

type

0

in the IRQ column next to the

irq

port.

4. On the File menu, click Save.

Specifying Exported Interfaces

Many interface signals in this Qsys system connect to modules outside the design.

Follow these steps to export an interface:

1. Click in the Export column.

2. First, accept the default name that appears in the Export column. Then, right-click

on the name, select Rename and type the name shown in

.

DUT

Txs

Avalon Memory Mapped Slave

dma_0

write_master

Avalon Memory Mapped Master

onchip_memory

s1

Avalon Memory Mapped Slave

dma_0

read_master

Avalon Memory Mapped Master

DUT

nreset_status

onchip_memory

reset1

DUT

nreset_status

dma_0

reset

DUT

nreset_status

clk0

clk_reset

clk_0 clk_reset

alt_xcvr_reconfig_0

mgmt_rst_reset

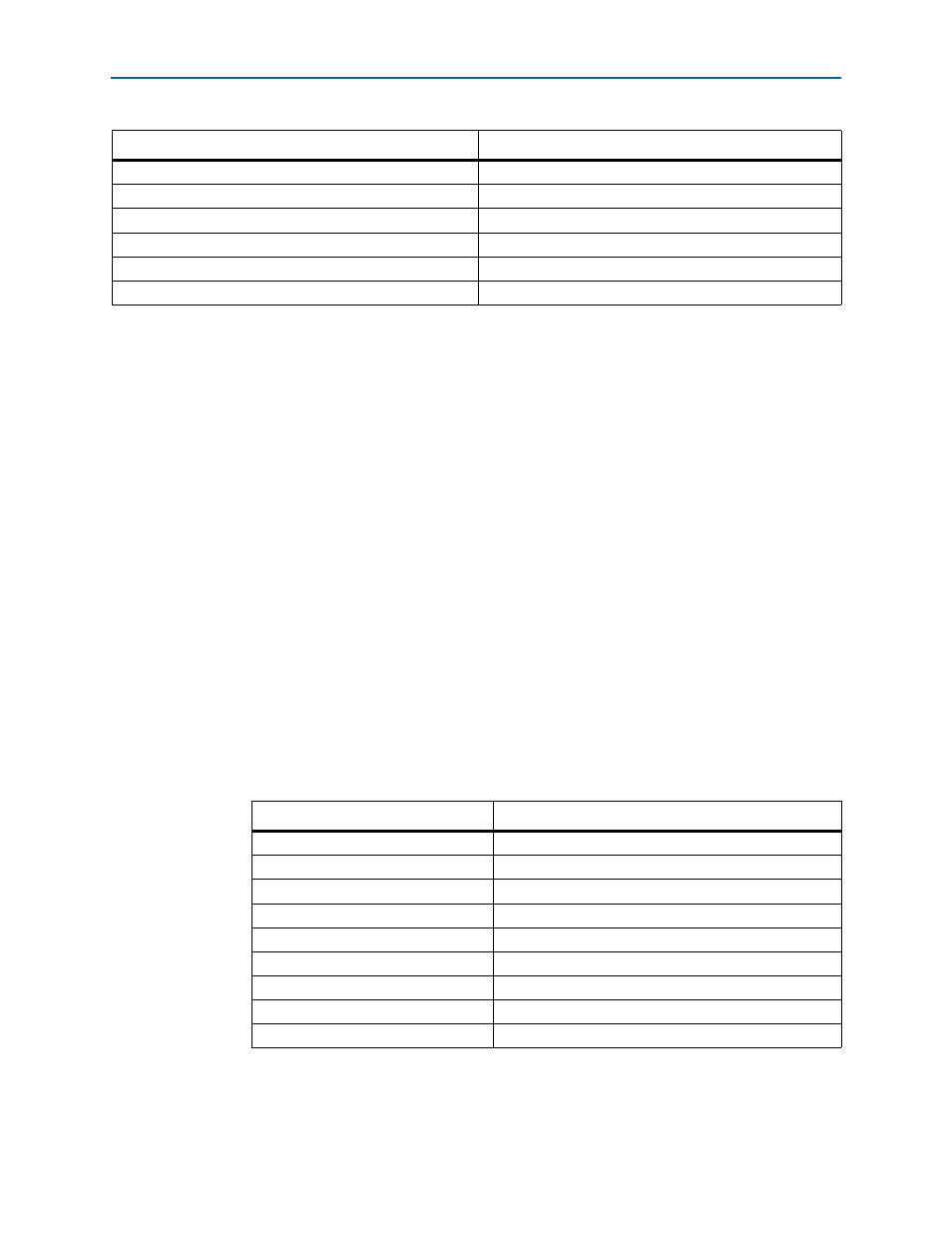

Table 3–11. Qsys Connections (Part 2 of 2)

Make Connection From:

To:

Table 3–12. Exported Interfaces

Interface Name

Exported Name

DUT

refclk

refclk

DUT

npor

npor

DUT

reconfig_clk_locked

pcie_svhip_avmm_0_reconfig_clk_locked

DUT

hip_serial

hip_serial

DUT

hip_pipe

hip_pipe

DUT

hip_ctrl

hip_ctrl

alt_xcvr_reconfig_0

reconfig_mgmt

alt_xcvr_reconfig_0_reconfig_mgmt

clk_0

clk_in

xcvr_reconfig_clk

clk_0

clk_in_reset

xcvr_reconfig_reset