Altera Arria V Hard IP for PCI Express User Manual

Page 114

7–16

Chapter 7: IP Core Interfaces

Arria V Hard IP for PCI Express

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

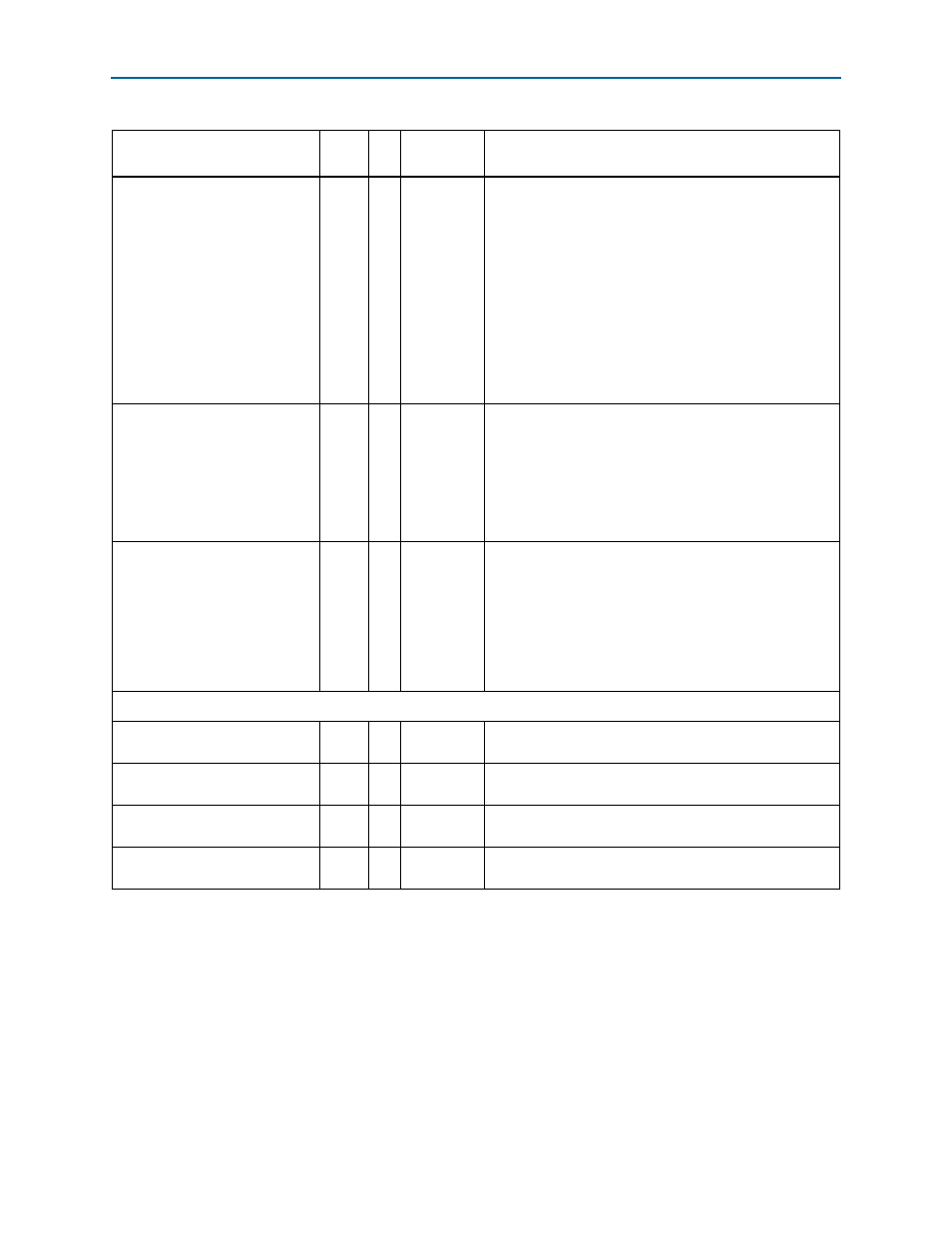

tx_st_valid

1

I

valid

Clocks

tx_st_data

to the Hard IP when

tx_st_ready

is

also asserted. Between

tx_st_sop

and

tx_st_eop

,

tx_st_valid

can be asserted only if

tx_st_ready

is

asserted. When

tx_st_ready

deasserts, this signal must

deassert within 1 or 2 clock cycles. When

tx_st_ready

reasserts, and

tx_st_data

is in mid-TLP, this signal must

reassert within 2 cycles. Refer to

for the timing of this signal.

To facilitate timing closure, Altera recommends that you

register both the

tx_st_ready

and

tx_st_valid

signals.

If no other delays are added to the ready-valid latency, the

resulting delay corresponds to a

readyLatency

of 2.

tx_st_empty

1

I

empty

Indicates the number of qwords that are empty during

cycles that contain the end of a packet. When asserted, the

empty qwords are in the high-order bits. Valid only when

tx_st_eop

is asserted.

Not used when

tx_st_data

is 64 bits. When asserted,

indicates that the upper qword is empty, does not contain

valid data.

tx_st_err

1

I

error

Indicates an error on transmitted TLP. This signal is used to

nullify a packet. It should only be applied to posted and

completion TLPs with payload. To nullify a packet, assert

this signal for 1 cycle after the SOP and before the EOP.

When a packet is nullified, the following packet should not

be transmitted until the next clock cycle.

tx_st_err

is not

available for packets that are 1 or 2 cycles long. The error

signal must be asserted while the valid signal is asserted.

Component Specific Signals

tx_fifo_empty

1

O

component

specific

When asserted high, indicates that the TX FIFO is empty.

tx_cred_datafccp

12

O

component

specific

Data credit limit for transmission of completions. Each

credit is 16 bytes.

tx_cred_datafcnp

12

O

component

specific

Data credit limit for transmission of non-posted requests.

Each credit is 16 bytes.

tx_cred_datafcp

12

O

component

specific

Data credit limit for transmission of posted writes. Each

credit is 16 bytes.

Table 7–4. 64- or 128-Bit Avalon-ST TX Datapath (Part 2 of 4)

Signal

Width

Dir

Avalon-ST

Type

Description