Altera Arria V Hard IP for PCI Express User Manual

Page 40

3–6

Chapter 3: Getting Started with the Avalon-MM Arria Hard IP for PCI Express

Adding the Remaining Components to the Qsys System

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

3. In the DMA Controller parameter editor, specify the parameters and conditions

listed in the following table.

4. Click Finish. The DMA Controller module is added to your Qsys system.

5. On the Component Library tab, type the following text string in the search box:

On Chip

r

Qsys filters the component library and shows all components matching the text

string you entered.

6. Click On-Chip Memory (RAM or ROM) and then click +Add. Specify the

parameters listed in the following table.

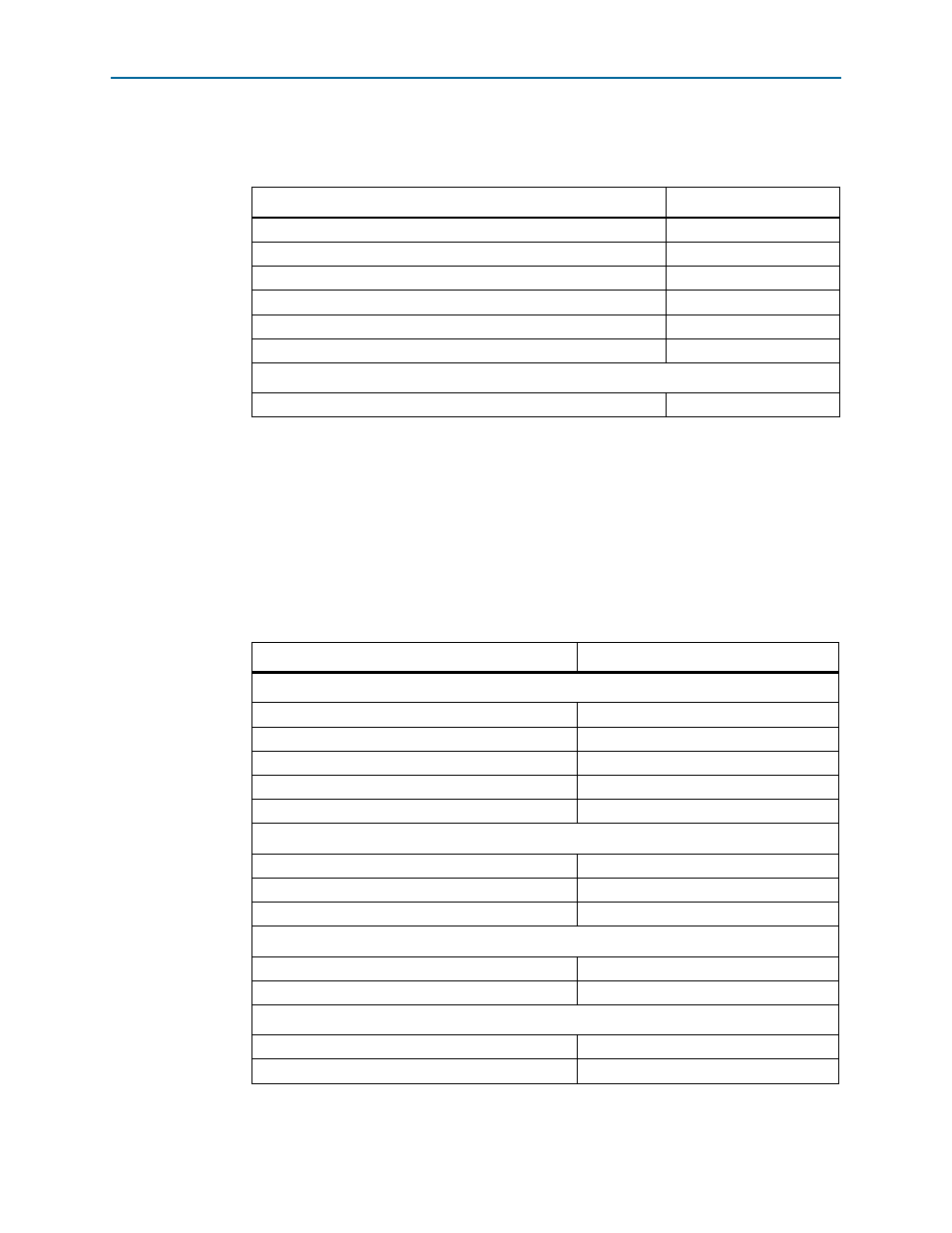

Table 3–8. DMA Controller Parameters

Parameter

Value

Width of the DMA length register

13

Enable burst transfers

Turn on this option

Maximum burst size

Select 128

Data transfer FIFO depth

Select 32

Construct FIFO from registers

Turn off this option

Construct FIFO from embedded memory blocks

Turn on this option

Advanced

Allowed Transactions

Turn on all options

Table 3–9. On-Chip Memory Parameters (Part 1 of 2)

Parameter

Value

Memory Type

Type

Select RAM (Writeable)

Dual-port access

Turn off this option

Single clock option

Not applicable

Read During Write Mode

Not applicable

Block type

Auto

Size

Data width

64

Total memory size

4096 Bytes

Minimize memory block usage (may impact f

MAX

)

Not applicable

Read latency

Slave s1 latency

1

Slave s2 latency

Not applicable

Memory initialization

Initialize memory content

Turn on this option

Enable non-default initialization file

Turn off this option