Altera Arria V Hard IP for PCI Express User Manual

Page 284

Info–2

Revision History

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

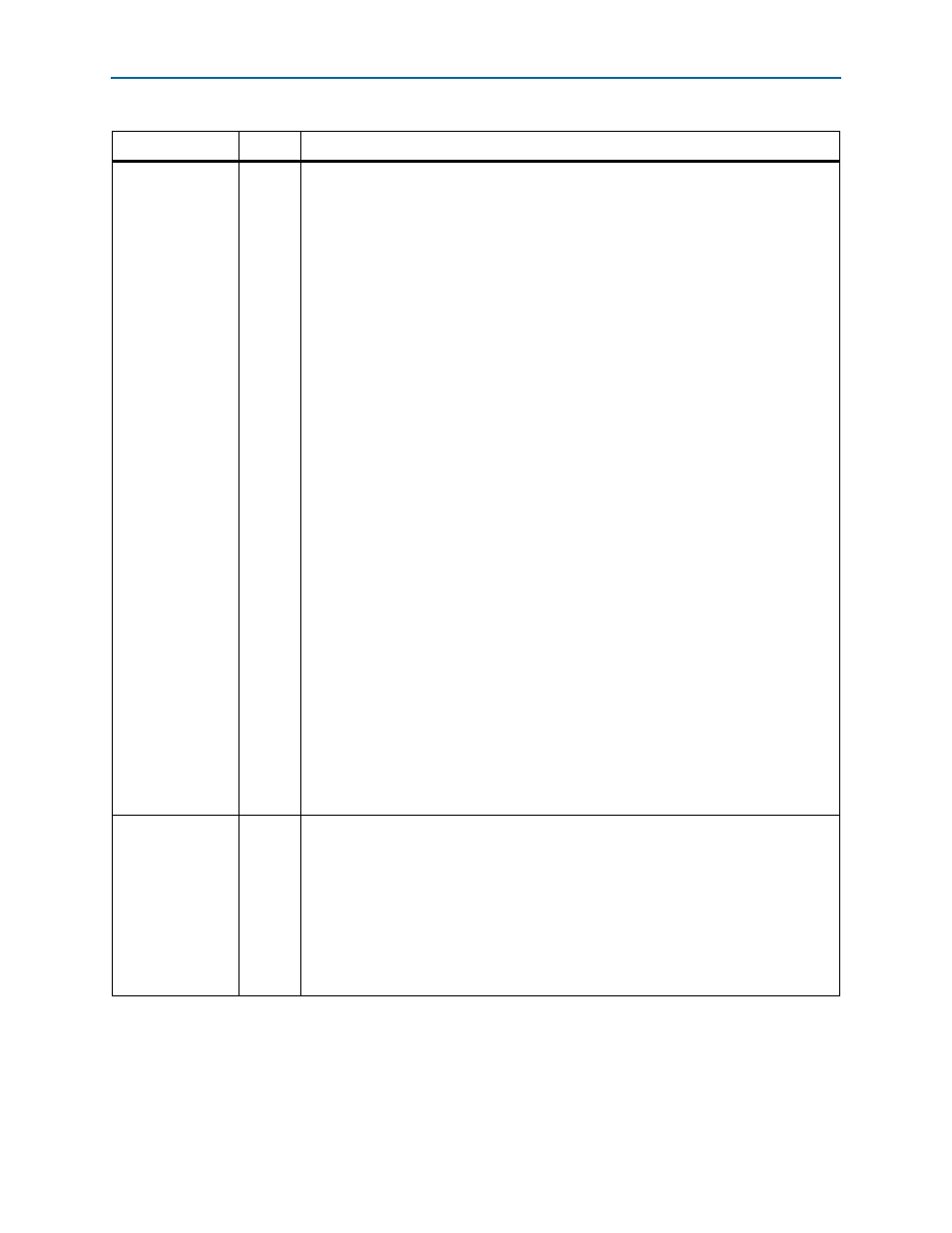

Date

Version

Changes Made

SPR

November 2013

13.1

■

Added constraints for

refclk

when CvP is enabled.

■

Corrected location information for

nPERSTL*

.

■

Corrected definition of test_in[4:1].

■

In Debugging chapter, under changing between soft and hard reset controller, changed

the file name in which the parameter

hip_hard_reset_hwtcl

must be set to 0 to use

the soft reset controller.

■

Added explanation of channel labeling for serial data. The Hard IP on the left side of the

device must connect to the appropriate channels on the left side of the device, and so

on.

■

Corrected connection for the Transceiver Reconfiguration Controller IP Core reset

signal, alt_xcvr_reconfig_0

mgmt_rst_reset

, in the Chapter 3, Getting Started with the

Avalon-MM Arria V Hard IP for PCI Express. This reset input connects to clk_0

clk_reset

.

■

Added definition of

nreset_status

for variants using the Avalon-MM interface.

■

In Transaction Layer Routing Rules and Programming Model for Avalon-MM Root Port ,

added the fact that Type 0 Configuration Requests sent to the Root Port are not filtered

by the device number. Application Layer software must filter out requests for device

number greater than 0.

■

Added Recommended Reset Sequence to Avoid Link Training Issues to the Debugging

chapter.

■

Added limitation for

RxmIrq_

[

:0]

when interrupts are received on

consecutive cycles.

■

Updated timing diagram for

tl_cfg_ctl

.

■

Removed I/O Read Request and I/O Write Requests from TLPs supported for Avalon-

MM interface.

■

Added note that the

dl_ltssm[4:0]

interface can be used for SignalTap debugging.

■

Added restriction on the use of dynamic transceiver reconfiguration when CvP is

enabled.

■

Added instructions to change between serial and PIPE simulation in the Debugging

chapter.

■

Removed

test_out

bus because it does not meet timing.

May 2013

13.0

■

Timing models are now final.

■

Added instructions for running the Single DWord variant.

■

Corrected definition of

test_in[4:1]

. This vector must be set to 4’b0100.

■

Corrected connection for

mgmt_clk_clk

in Figure 3-2.

■

Corrected definition of

nPERSTL*

. The device has 1

nPERSTL*

pin for each instance of

the Hard IP for PCI Express in the device.

■

Corrected feature comparison table in Datasheet chapter. The Avalon-MM Hard IP for

PCI Express IP Core does not support legacy endpoints.