Altera Arria V Hard IP for PCI Express User Manual

Page 275

Chapter 18: Debugging

18–5

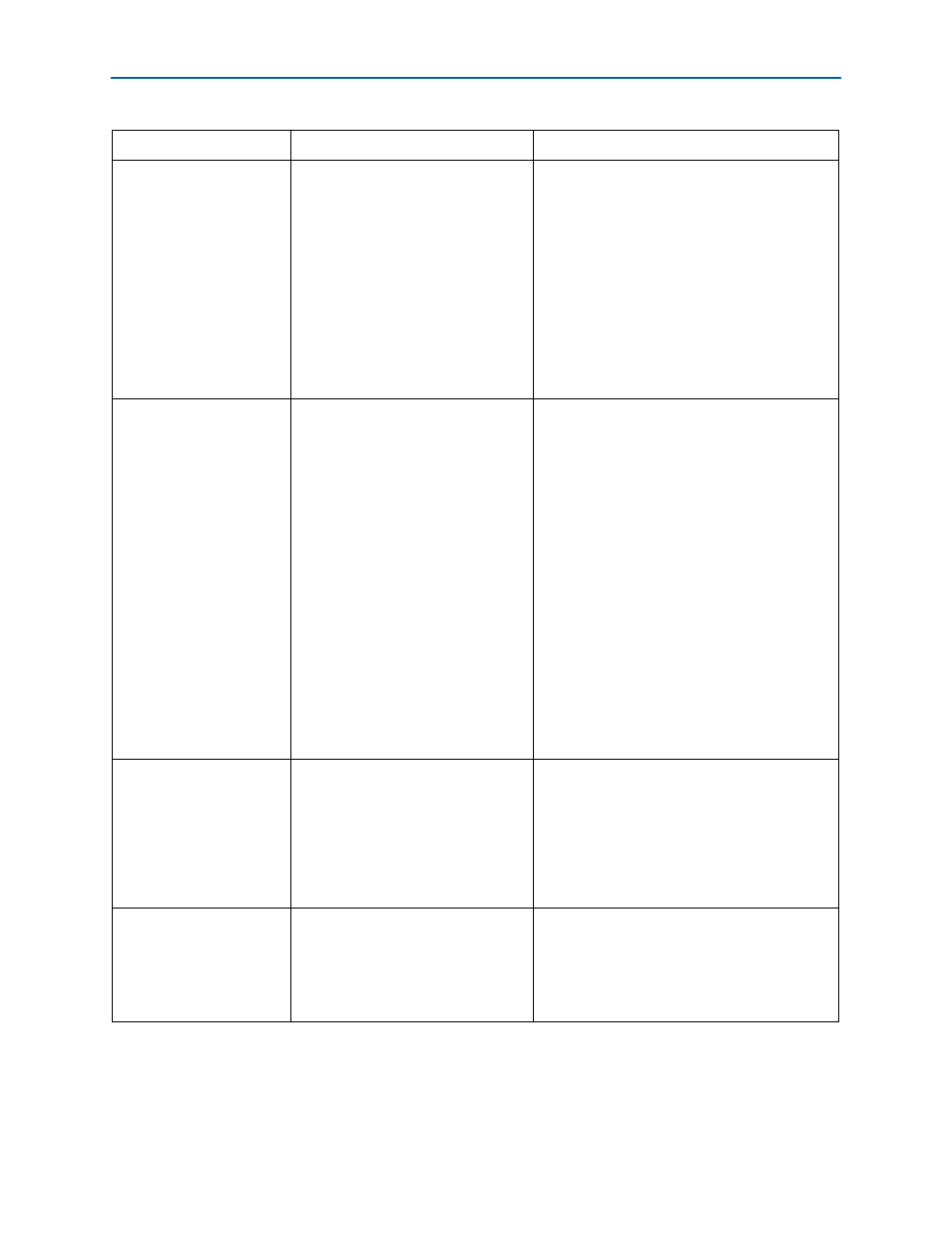

Link Hangs in L0 Due To Deassertion of tx_st_ready

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

f

For more information about link training, refer to the “Link Training and Status State

Machine (LTSSM) Descriptions” section of

Flow control credit

overflows

Determine if the credit field associated

with the current TLP type in the

tx_cred

bus is less than the requested

credit value. When insufficient credits

are available, the core waits for the link

partner to release the correct credit

type. Sufficient credits may be

unavailable if the link partner

increments credits more than expected,

creating a situation where the Arria V

Hard IP for PCI Express IP Core credit

calculation is out-of-sink with its link

partner.

Add logic to detect conditions where the

tx_st_ready

signal remains deasserted for more

than 100 cycles. Set post-triggering conditions to

check the value of the

tx_cred*

and

tx_st_*

interfaces. Add a FIFO status signal to determine if

the TXFIFO is full.

Malformed TLP is

transmitted

Refer to the log file to find the last good

packet transmitted on the link. Correlate

this packet with TLP sent on Avalon-ST

interface. Determine if the last TLP sent

has any of the following errors:

■

The actual payload sent does not

match the length field.

■

The byte enable signals violate rules

for byte enables as specified in the

.

■

The format and type fields are

incorrectly specified.

■

TD field is asserted, indicating the

presence of a TLP digest (ECRC),

but the ECRC dword is not present at

the end of TLP.

■

The payload crosses a 4KByte

boundary.

Revise the Application Layer logic to correct the

error condition.

Insufficient Posted credits

released by Root Port

If a Memory Write TLP is transmitted

with a payload greater than the

maximum payload size, the Root Port

may release an incorrect posted data

credit to the End Point in simulation. As

a result, the End Point does not have

enough credits to send additional

Memory Write Requests.

Make sure Application Layer sends Memory Write

Requests with a payload less than or equal the

value specified by the maximum payload size.

Missing completion packets

or dropped packets

The RX Completion TLP might cause

the RX FIFO to overflow. Make sure that

the total outstanding read data of all

pending Memory Read Requests is

smaller than the allocated completion

credits in RX buffer.

You must ensure that the data for all outstanding

read requests does not exceed the completion

credits in the RX buffer.

Table 18–2. Link Hangs in L0 (Part 2 of 2)

Possible Causes

Symptoms and Root Causes

Workarounds and Solutions