Understanding the files generated, Simulating the example design – Altera Arria V Hard IP for PCI Express User Manual

Page 27

Chapter 2: Getting Started with the Arria Hard IP for PCI Express

2–11

Qsys Design Flow

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

Understanding the Files Generated

The following table provides an overview of the files and directories Qsys generates.

Simulating the Example Design

Follow these steps to compile the testbench for simulation and run the chaining DMA

testbench.

1. Start your simulation tool. This example uses the ModelSim

®

software.

2. From the ModelSim transcript window, in the testbench directory

(./example_design/altera_pcie_

type the following commands:

a.

do msim_setup.tcl

r

b. h

r (This is the ModelSim help command.)

c. ld_debug

r (This command compiles all design files and elaborates the

top-level design without any optimization.)

d. run -all

r

The following example shows a partial transcript from a successful simulation. As this

transcript illustrates, the simulation includes the following stages:

■

Link training

■

Configuration

■

DMA reads and writes

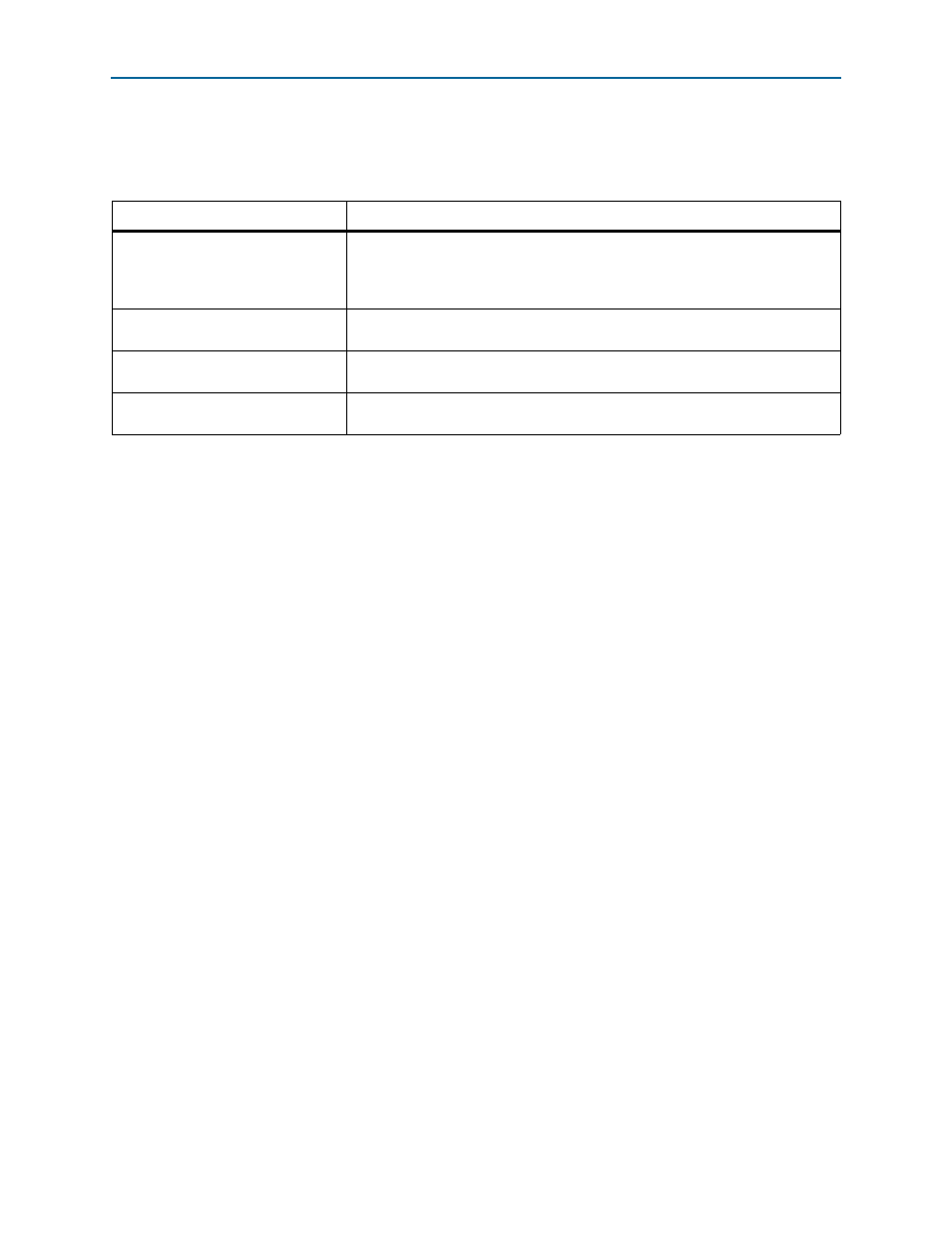

Table 2–10. Qsys Generation Output Files

Directory

Description

includes the top-level HDL file for the Hard I for PCI Express and the .qip file that

lists all of the necessary assignments and information required to process the IP

core in the Quartus II compiler. Generally, a single .qip file is generated for each IP

core.

Includes the HDL files necessary for Quartus II synthesis.

Includes testbench subdirectories for the Aldec, Cadence and Mentor simulation

tools with the required libraries and simulation scripts.

Includes the HDL source files and scripts for the simulation testbench.