Optional features, Configuration via protocol (cvp), Chapter 12. optional features – Altera Arria V Hard IP for PCI Express User Manual

Page 203: Configuration via protocol (cvp) –1

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

12. Optional Features

This chapter provides information on several additional topics. It includes the

following sections:

■

Configuration via Protocol (CvP)

■

■

Lane Initialization and Reversal

Configuration via Protocol (CvP)

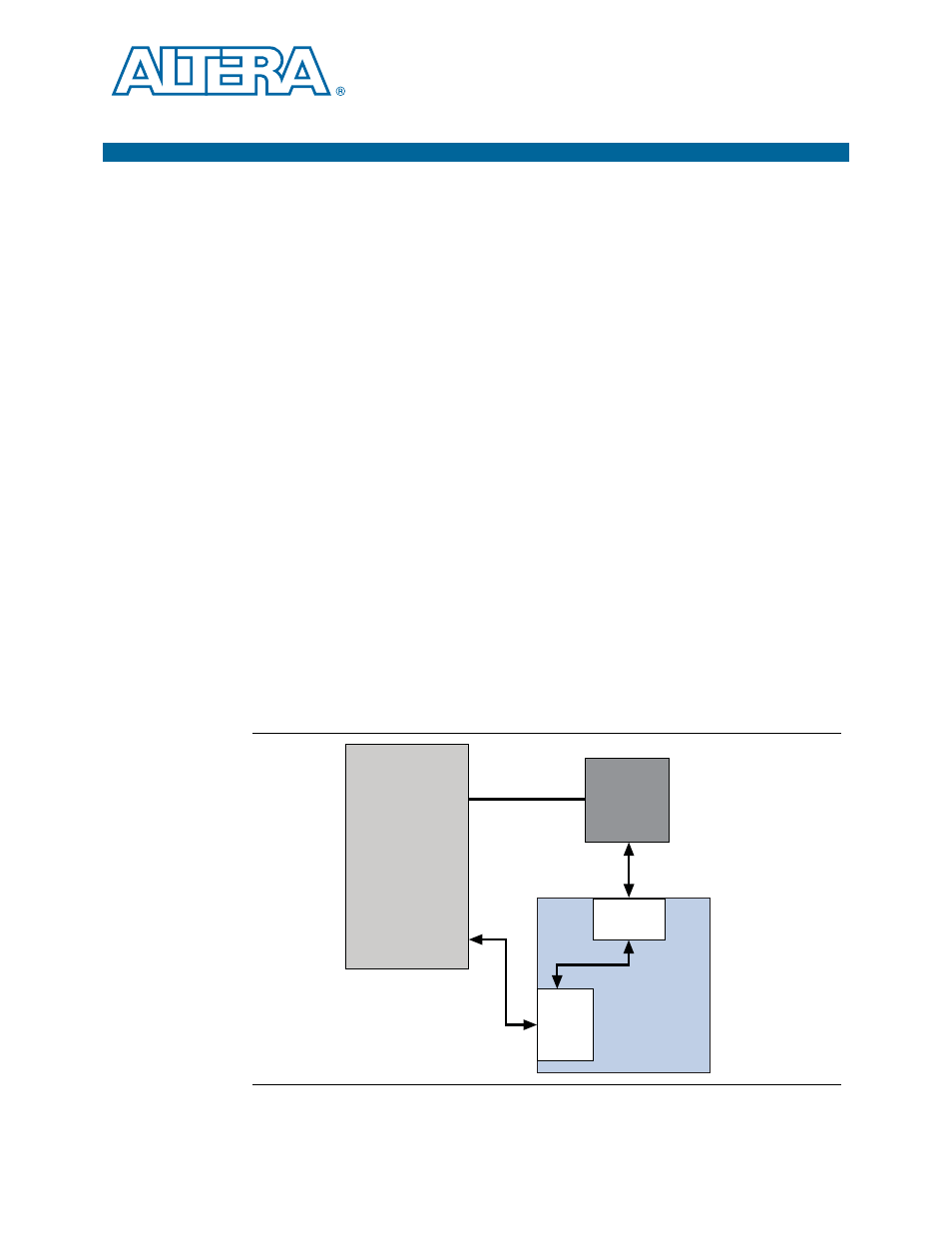

The Arria V architecture includes an option for sequencing the processes that

configure the FPGA and initialize the PCI Express link. In prior devices, a single

Program Object File (.pof) programmed the I/O ring and FPGA fabric before the PCIe

link training and enumeration began. In Arria V, the .pof file is divided into two

parts:

■

The I/O bitstream contains the data to program the I/O ring and the Hard IP for

PCI Express.

■

The core bitstream contains the data to program the FPGA fabric.

In Arria V devices, the I/O ring and PCI Express link are programmed first, allowing

the PCI Express link to reach the L0 state and begin operation independently, before

the rest of the core is programmed

.

After the PCI Express link is established, it can be

used to program the rest of the device. Programming the FPGA fabric using the PCIe

link is called Configuration via Protocol (CvP).

Figure 12–1

shows the blocks that

implement CvP.

Figure 12–1. CvP in Arria V Devices

USB Port

PCIe Port

Arria V or

Cyclone V Device

Host CPU

Config Cntl

Block

Active Serial or

Active Quad

Device Configuration

Download cable

PCIe Link

used for

Configuration

via Protocol (CvP)

Serial or

Quad Flash

Hard IP

for PCIe

December 2013

UG-01110-1.5