Test signals, Test signals –54 – Altera Arria V Hard IP for PCI Express User Manual

Page 153

Chapter 7: IP Core Interfaces

7–55

Test Signals

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

Test Signals

The

test_in

bus provides run-time control and monitoring of the internal state of the

Arria V Hard IP for PCI Express.

c

Altera recommends that you use the

test_in

signals for debug or non-critical status

monitoring purposes such as LED displays of PCIe link status. They should not be

used for design function purposes. Use of these signals will make it more difficult to

close timing on the design. The test signals have not been rigorously verified and will

not function as documented in some corner cases.

describes the

test_in

bus signals. In Qsys these signals have the prefix,

hip_ctrl_.

txmargin0[2:0]

O

Selects the TX V

OD

settings. The following settings are defined:

■

3'b000: Normal operating range

■

3'b001: Full swing: 800 - 1200 mV, Half swing: 400 - 700 mV

■

3'b010: Reserved

■

3'b011: Reserved

■

3'b100: Full swing: 200 - 400 mV Half swing: 100 - 200 mV if the last

value or vendor defined

■

3'b101: Full swing: 200 - 400 mV Half swing: 100 - 200 mV

■

3'b110: Full swing: 200 - 400 mV Half swing: 100 - 200 mV

■

3'b111: Full swing: 200 - 400 mV, Half swing: 100 - 200 mV

Notes to

:

(1) Signals that include lane number 0 also exist for lanes 1-7.

(2) These signals are for simulation only. For Quartus II software compilation, these pipe signals can be left floating.

Table 7–26. PIPE Interface Signals (Part 4 of 4)

Signal I/O

Description

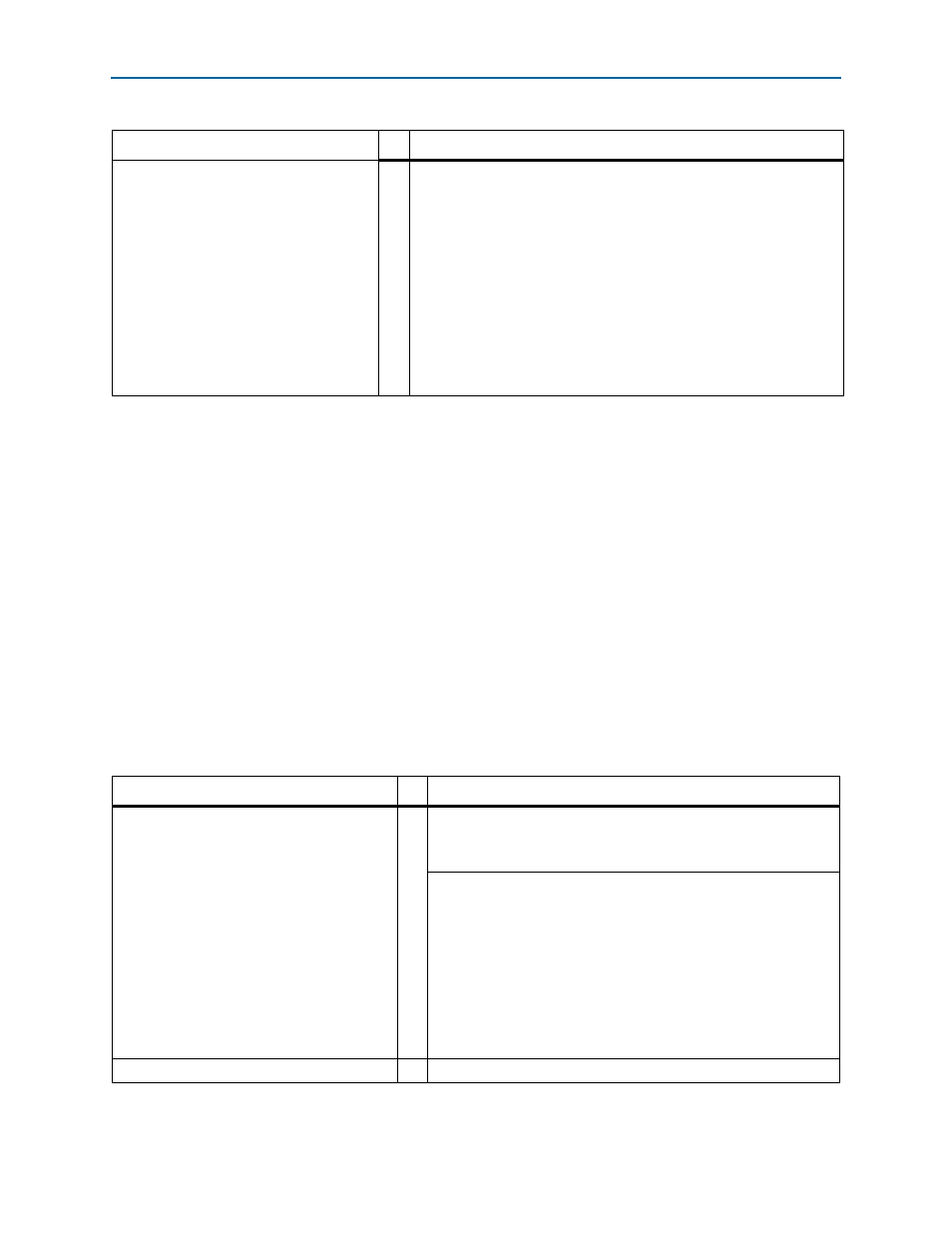

Table 7–27. Test Interface Signals

Signal

I/O

Description

test_in[31:0]

I

[0]–Simulation mode. This signal can be set to 1 to accelerate

initialization by reducing the value of many initialization counters.

[4:1] Reserved. Must be set to 4’b0100.

[6:5] Compliance test mode. Disable/force compliance mode:

■

bit 0–When set, prevents the LTSSM from entering compliance

mode. Toggling this bit controls the entry and exit from the

compliance state, enabling the transmission of Gen1 and Gen2

compliance patterns.

■

bit 1–Forces compliance mode. Forces entry to compliance mode

when timeout is reached in polling.active state (and not all lanes

have detected their exit condition).

■

[31:7] Reserved.

simu_mode_pipe

O

When set to 1, the PIPE interface is in simulation mode.