Altera Arria V Hard IP for PCI Express User Manual

Page 76

6–2

Chapter 6: IP Core Architecture

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

As

Figure 6–1

illustrates, an Avalon-ST interface provides access to the Application

Layer which can be either 64 or 128 bits.

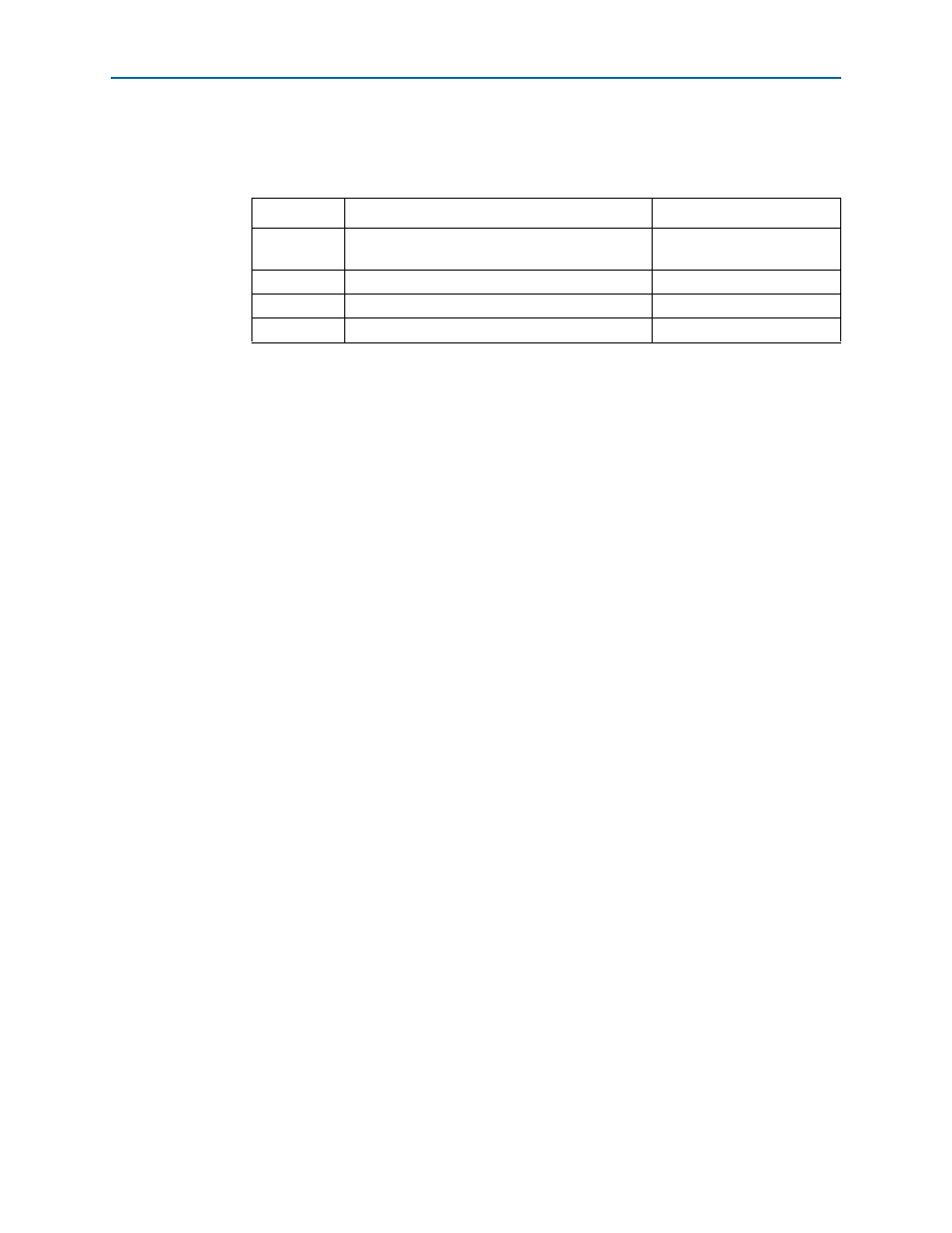

Table 6–1

provides the Application Layer

clock frequencies.

The following interfaces provide access to the Application Layer’s Configuration

Space Registers:

■

The LMI interface

■

For Root Ports, you can also access the Configuration Space Registers with a

Configuration Type TLP using the Avalon-ST interface. A Type 0 Configuration

TLP is used to access the Root Port Configuration Space Registers, and a Type 1

Configuration TLP is used to access the Configuration Space Registers of

downstream components, typically Endpoints on the other side of the link.

The Hard IP includes dedicated clock domain crossing logic (CDC) between the

PHYMAC and Data Link Layers.

This chapter provides an overview of the architecture of the Arria V Hard IP for PCI

Express. It includes the following sections:

■

■

■

■

■

■

Single DWord Completer Endpoint

Table 6–1. Application Layer Clock Frequencies

Lanes

Gen1

Gen2

×1

125 MHz @ 64 bits or

62.5 MHz @ 64 bits

125 MHz @ 64 bits

×2

125 MHz @ 64 bits

125 MHz @ 64 bits

×4

125 MHz @ 64 bits

125 MHz @ 128 bits

×8

125 MHz @ 128 bits

—