Through, Figure 7–21, Figure 7–20 on – Altera Arria V Hard IP for PCI Express User Manual

Page 117: For the timing of

Chapter 7: IP Core Interfaces

7–19

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

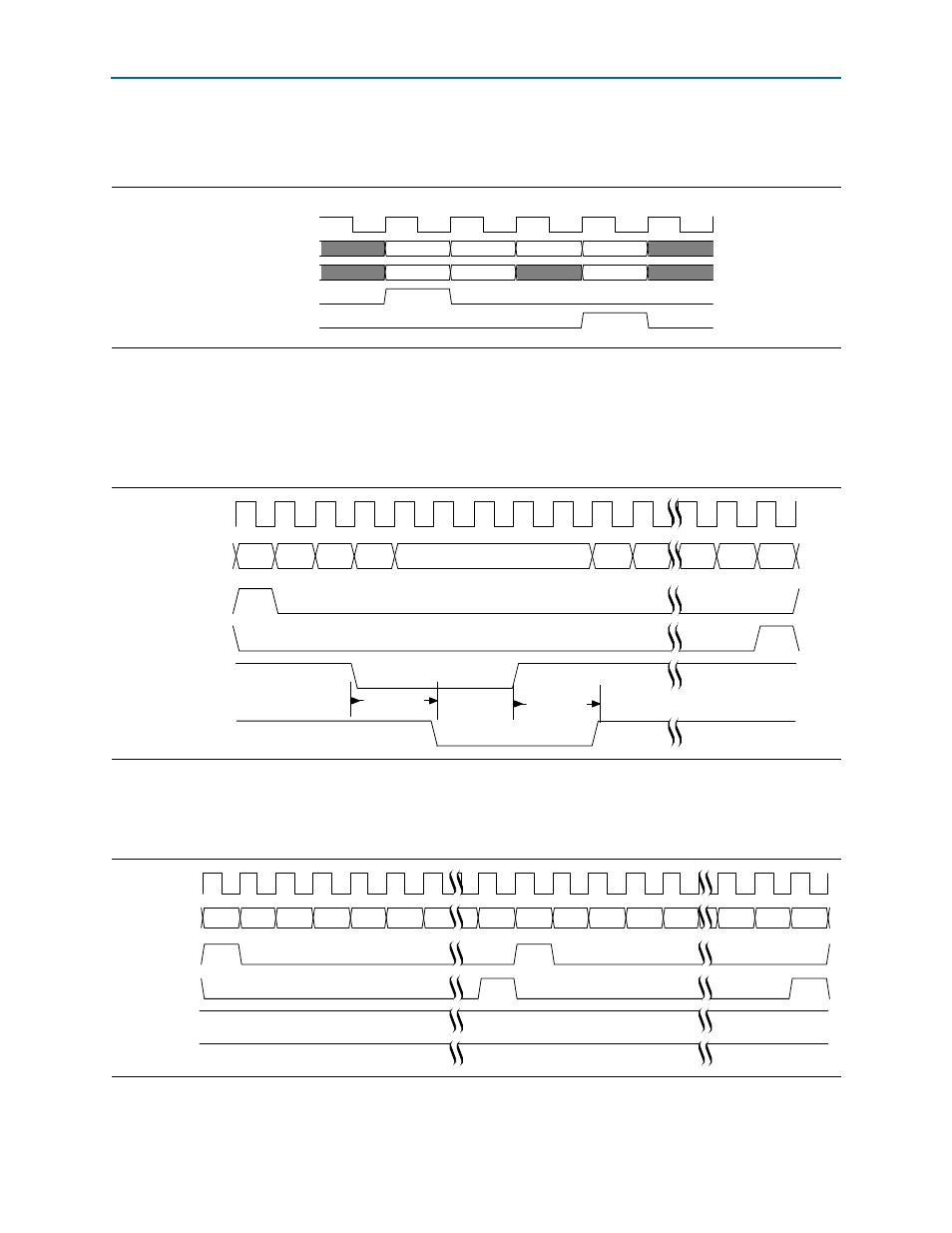

illustrates the mapping between Avalon-ST TX packets and PCI Express

TLPs for four dword header with non-qword aligned addresses with a 64-bit bus.

illustrates the timing of the TX interface when the Arria V Hard IP for

PCI Express IP core backpressures the Application Layer by deasserting

tx_st_ready

.

Because the

readyLatency

is two cycles, the Application Layer deasserts

tx_st_valid

after two cycles and holds

tx_st_data

until two cycles after

tx_st_ready

is asserted.

illustrates back-to-back transmission of 64-bit packets with no intervening

dead cycles between the assertion of

tx_st_eop

and

tx_st_sop

.

Figure 7–19. 64-Bit Avalon-ST tx_st_data Cycle Definition for TLP 4-Dword Header with Non-Qword Aligned Address

coreclkout

tx_st_data[63:32]

tx_st_data[31:0]

tx_st_sop

tx_st_eop

Header 1

Header3

Data0

Data2

Header 0

Header2

Data1

Figure 7–20. 64-Bit Transaction Layer Backpressures the Application Layer

coreclkout

tx_st_sop

tx_st_eop

tx_st_ready

tx_st_valid

tx_st_data[63:0]..

.

.

.

.

.

.

.

.

00. .

00 ...

BB...

BB ...

BBBB0306BBB0305A

BB ... BB ...

BB ... BB ... BB....

readyLatency

readyLatency

Figure 7–21. 64-Bit Back-to-Back Transmission on the TX Interface

coreclkout

tx_st_sop

tx_st_eop

tx_st_ready

tx_st_valid

tx_st_data[63:0]

01

. 00

. BB . BB . BB . BB . B

.

. BB . 01

. 00

. CC . CC . CC .

CC . CC . CC .