Altera Arria V Hard IP for PCI Express User Manual

Page 21

Chapter 2: Getting Started with the Arria Hard IP for PCI Express

2–5

Customizing the Endpoint in the MegaWizard Plug-In Manager Design Flow

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

10. On the Error Reporting tab, leave all options off.

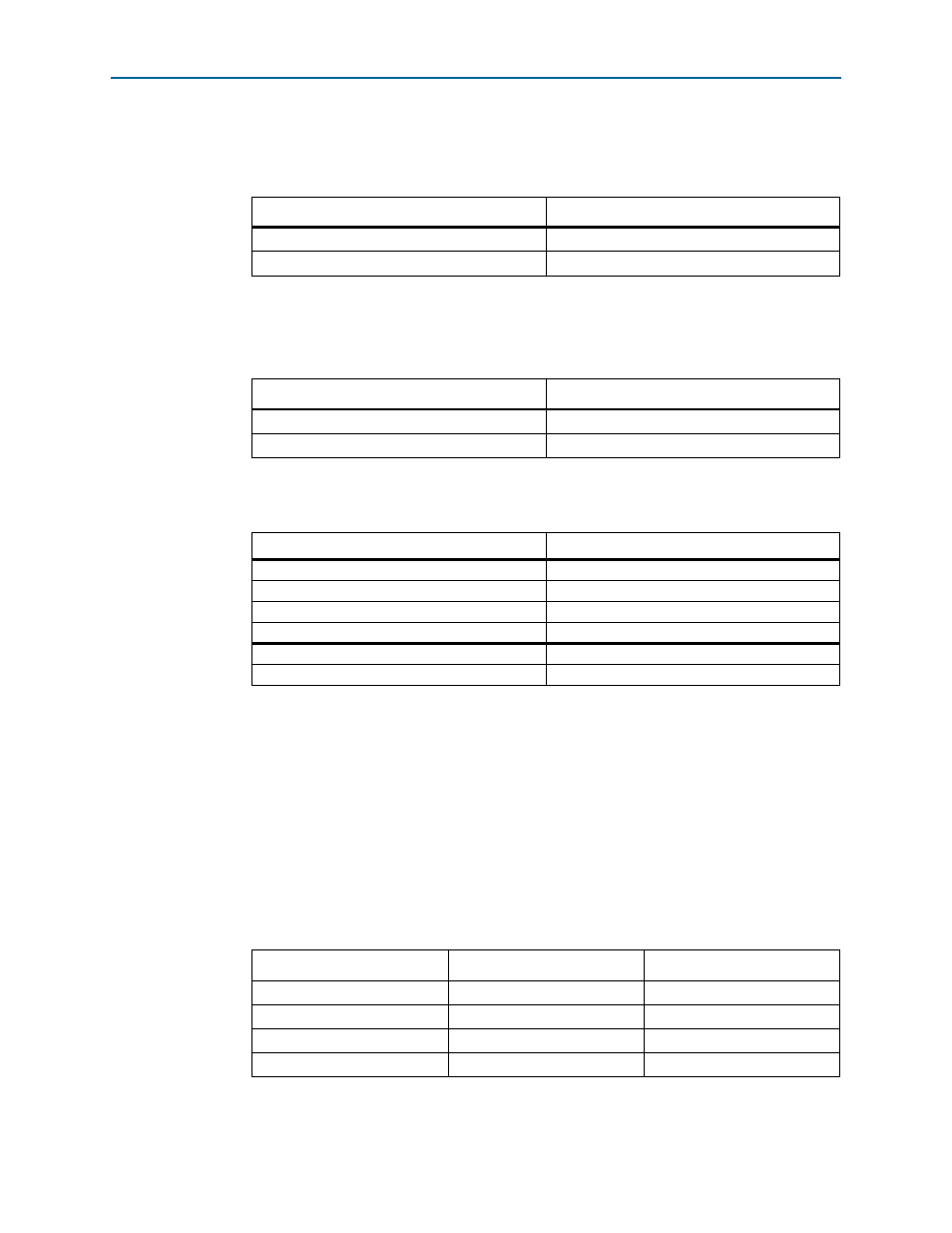

11. Specify the Link settings listed in

Table 2–7

.

12. On the Slot Capabilities tab, leave the Slot register turned off.

13. Specify the Power Management parameters listed in

Table 2–4

.

14. Specify the BAR settings for Func0 listed in

Table 2–5

.

15. You can leave Func0 BAR3 through Func

16. 0 BAR5 and the Func0 Expansion ROM Disabled.

17. Under the Base and Limit Registers heading, disable both the Input/Output and

Prefetchable memory

options. (These options are for Root Ports.)

18. For the Device ID Registers for Func0, specify the values listed in the center

column of

Table 2–6

. The right-hand column of this table lists the value assigned to

Altera devices. You must use the Altera values to run the reference design

described in

. Be sure to use

your company’s values for your final product.

Table 2–3. Link Tab

Parameter

Value

Link port number

1

Slot clock configuration

On

Table 2–4. Power Management Parameters

Parameter

Value

Endpoint L0s acceptable exit latency

Maximum of 64 ns

Endpoint L1 acceptable latency

Maximum of 1 µs

Table 2–5. Base Address Registers for Func0

Parameter

Value

BAR0 Type

64-bit prefetchable memory

BAR0 Size

256 MBytes - 28 bits

BAR1 Type

Disabled

BAR1 Size

N/A

BAR2 Type

32-bit non-prefetchable memory

BAR2 Size

1 KByte - 10 bits

Table 2–6. Device ID Registers for Func0

Register Name

Value

Altera Value

Vendor ID

0x00000000

0x00001172

Device ID

0x00000001

0x0000E001

Revision ID

0x00000001

0x00000001

Class Code

0x00000000

0x00FF0000