Altera Arria V Hard IP for PCI Express User Manual

Page 87

Chapter 6: IP Core Architecture

6–13

PCI Express Avalon-MM Bridge

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

■

Control Register Access (CRA) Slave Module—This optional, 32-bit Avalon-MM

dynamic addressing slave port provides access to internal control and status

registers from upstream PCI Express devices and external Avalon-MM masters.

Implementations that use MSI or dynamic address translation require this port.

When you select the Single dword completer in the GUI for the Avalon-MM Hard IP

for PCI Express, Qsys substitutes a unpipelined, 32-bit RX master port for the 64- or

128-bit full-featured RX master port. For more information about the 32-bit RX master

refer to

“Avalon-MM RX Master Block” on page 6–23

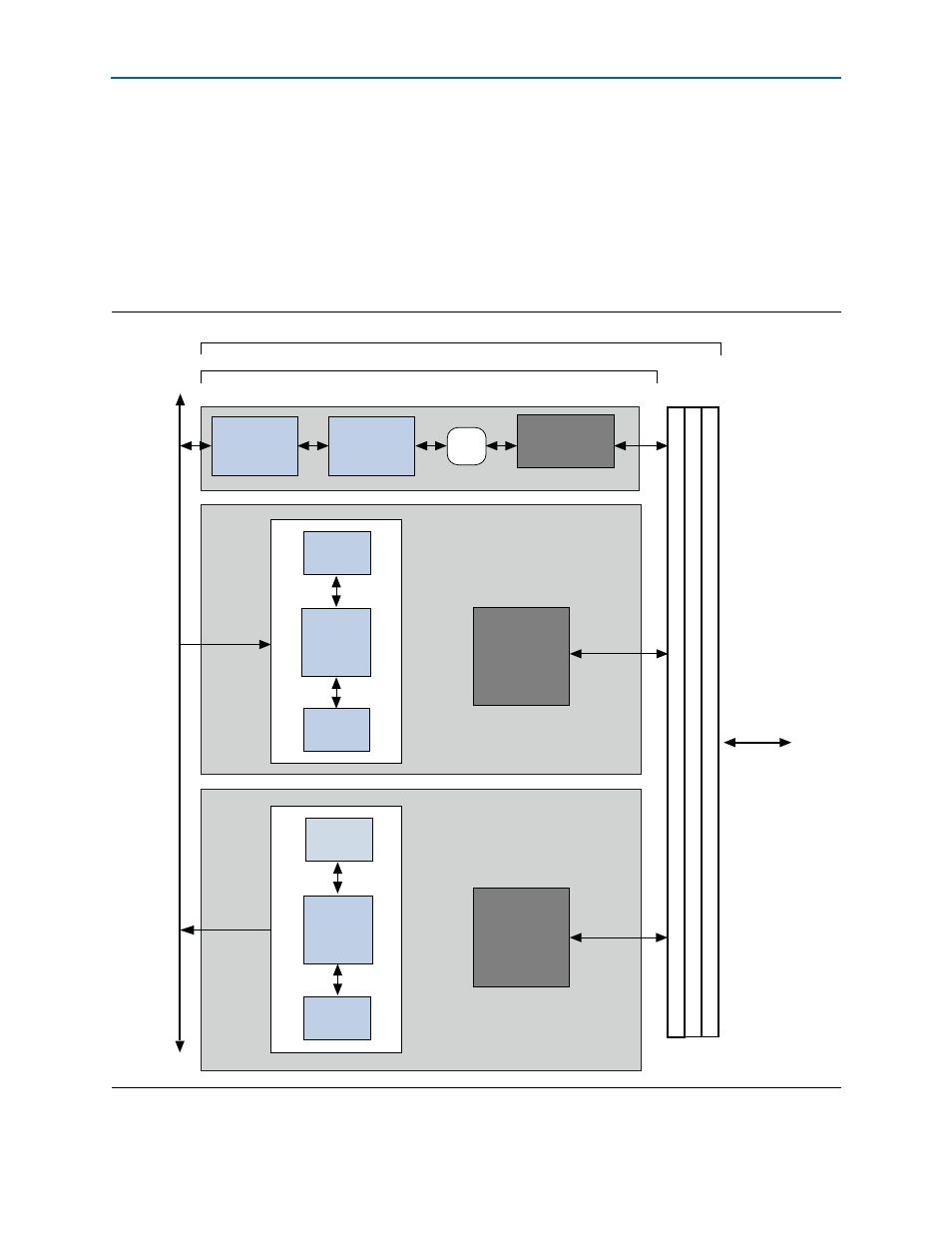

Figure 6–6

shows the block diagram of a PCI Express Avalon-MM bridge.

Figure 6–6. PCI Express Avalon-MM Bridge

Transaction Layer

PCI Express

Tx Controller

PCI Express

Rx Controller

Data Link Layer

Physical Layer

PCI Express MegaCore Function

Tx Slave Module

Control & Status

Reg (CSR)

Sync

Avalon Clock Domain

PCI Express Clock Domain

Rx Master Module

Rx Master Module

PCI Express Avalon-MM Bridge

System Interconnect Fabric

PCI Link

CRA Slave Module

Address

Translator

Avalon-MM

Tx Read

Response

Avalon-MM

Tx Slave

Avalon-MM

Rx Read

Response

Avalon-MM

Rx Master

MSI or

Legacy Interrupt

Generator

Control Register

Access Slave

Address

Translator