Altera Arria V Hard IP for PCI Express User Manual

Page 272

18–2

Chapter 18: Debugging

Link Training

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

You can use SignalTap II Embedded Logic Analyzer to diagnose the LTSSM state

transitions that are occurring and the PIPE interface. The

ltssmstate[4:0]

bus

encodes the status of LTSSM. The LTSSM state machine reflects the Physical Layer’s

progress through the link training process. For a complete description of the states

these signals encode, refer to

“Reset Signals” on page 8–29

. When link training

completes successfully and the link is up, the LTSSM should remain stable in the L0

state.

When link issues occur, you can monitor

ltssmstate[4:0]

to determine one of two

cases:

■

The link training fails before reaching the L0 state. Refer to

Table 18–1

for possible

causes of the failure to reach L0.

■

The link is initially established (L0), but then stalls with

tx_st_ready

deasserted

for more than 100 cycles. Refer to

Table 18–2 on page 18–4

for possible causes.

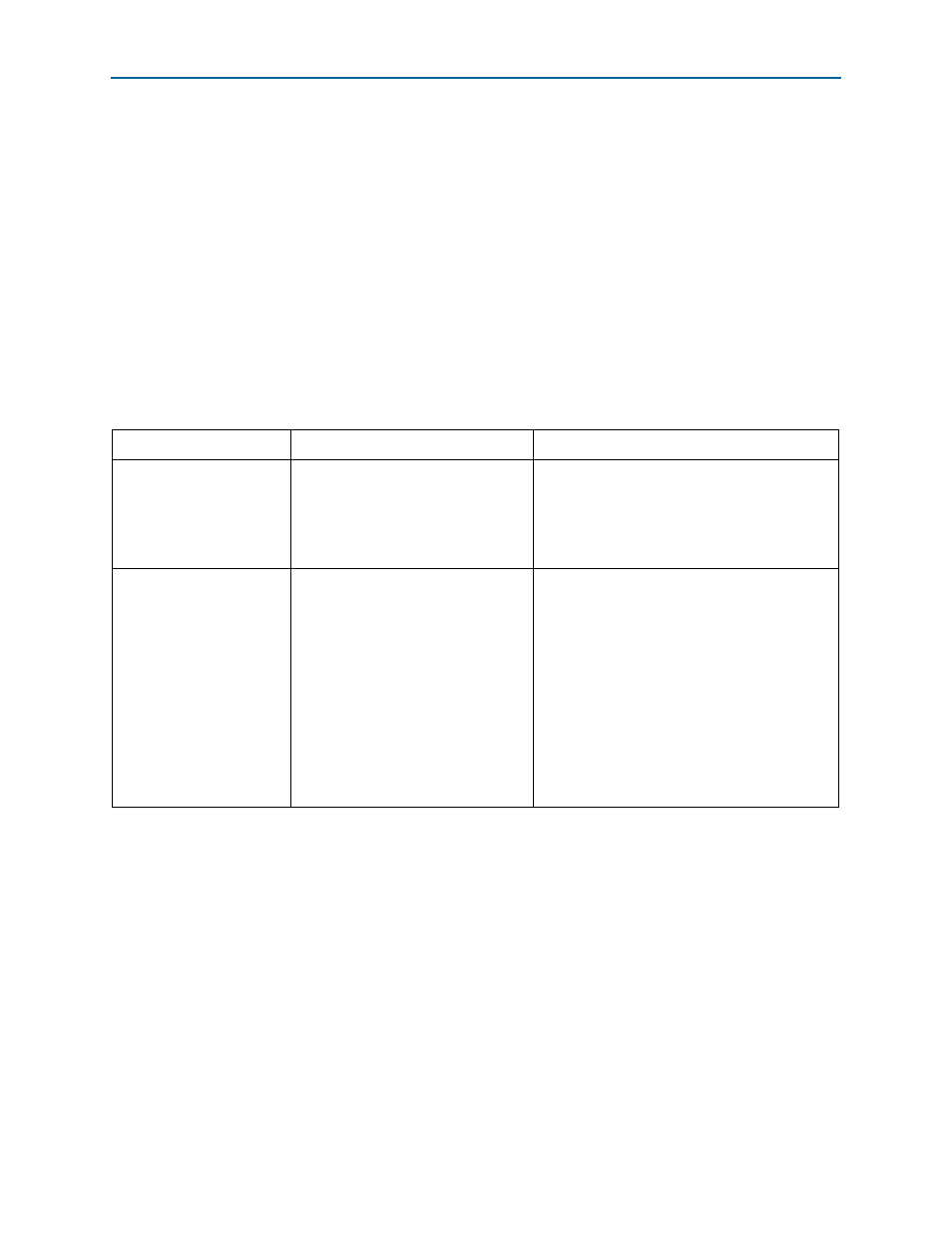

Table 18–1. Link Training Fails to Reach L0 (Part 1 of 3)

Possible Causes

Symptoms and Root Causes

Workarounds and Solutions

Link fails the Receiver

Detect sequence.

LTSSM toggles between

Detect.Quiet(0) and Detect.Active(1)

states

Check the following termination settings:

■

The on-chip termination (OCT) must be set to

100 ohm, with 0.1 uF capacitors on the TX pins.

■

Link partner RX pins must also have 100 ohm

termination.

Link fails with LTSSM stuck

in Detect.Active state (1)

This behavior may be caused by a PMA

issue if the host interrupts the Electrical

Idle state as indicated by high to low

transitions on the RxElecIdle

(

rxelecidle)

signal when

TxDetectRx=0 (

txdetectrx0)

at PIPE

interface. Check if OCT is turned off by

a Quartus Settings File (.qsf)

command. PCIe requires that OCT must

be used for proper Receiver Detect with

a value of 100 Ohm. You can debug this

issue using SignalTap II and

oscilloscope.

For Arria V devices, a workaround is

implemented in the reset sequence.