Device, Device –4 – Altera Arria V Hard IP for PCI Express User Manual

Page 56

4–4

Chapter 4: Parameter Settings for the Arria V Hard IP for PCI Express

Port Functions

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

Device

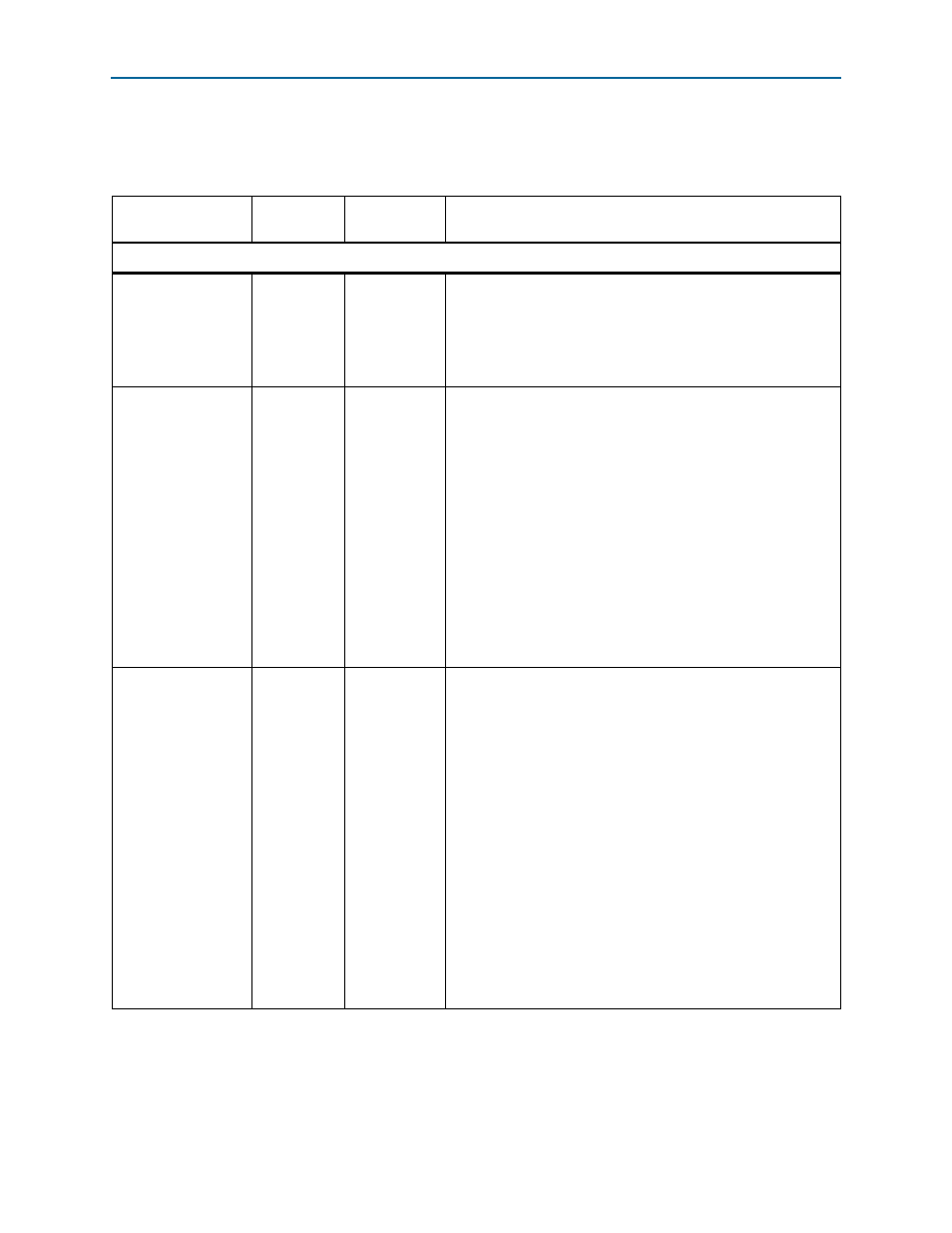

Table 4–2

describes the shared device parameters.

Table 4–2. Capabilities Registers for Function

Parameter

Possible

Values

Default

Value

Description

Device Capabilities

Maximum

payload size

128

bytes

256

bytes,

512

bytes,

128 bytes

Specifies the maximum payload size supported. This

parameter sets the read-only value of the max payload size

supported field of the Device Capabilities register (

optimizes the IP core for this size payload. You should

optimize this setting based on your typical expected

transaction sizes.

Number of tags

supported

supported per

function

32

64

32

Indicates the number of tags supported for non-posted

requests transmitted by the Application Layer. This parameter

sets the values in the Device Capabilities register (0x084) of

the PCI Express Capability Structure described in

The Transaction Layer tracks all outstanding completions for

non-posted requests made by the Application Layer. This

parameter configures the Transaction Layer for the maximum

number to track. The Application Layer must set the tag

values in all non-posted PCI Express headers to be less than

this value. The Application Layer can only use tag numbers

greater than 31 if configuration software sets the

Extended

Tag Field Enable

bit of the

Device Control

register.

This bit is available to the Application Layer as

cfg_devcsr[8]

.

Completion

timeout range

ABCD

BCD

ABC

AB

B

A

None

ABCD

Indicates device function support for the optional completion

timeout programmability mechanism. This mechanism allows

system software to modify the completion timeout value. This

field is applicable only to Root Ports and Endpoints that issue

requests on their own behalf. This parameter sets the values

in the

Device Capabilities 2

register (0xA4) of the PCI

Express Capability Structure Version 2.1 described in

. For all other functions, the value is

None. Four time value ranges are defined:

■

Range A: 50 µs to 10 ms

■

Range B: 10 ms to 250 ms

■

Range C: 250 ms to 4 s

■

Range D: 4 s to 64 s

Bits are set to show timeout value ranges supported. 0x0000b

completion timeout programming is not supported and the

function must implement a timeout value in the range 50 s to

50 ms.