Transceiver reconfiguration, Serial interface signals – Altera Arria V Hard IP for PCI Express User Manual

Page 145

Chapter 7: IP Core Interfaces

7–47

Physical Layer Interface Signals

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

Transceiver Reconfiguration

describes the transceiver support signals. In

,

of lanes.

f

For more information about the Transceiver Reconfiguration Controller, refer to the

“Transceiver Reconfiguration Controller” chapter in the

The following sections describe signals for the serial or parallel PIPE interfaces. The

PIPE interface is only available for simulation.

Serial Interface Signals

describes the serial interface signals.

f

Refer to

pin-out tables for all Altera devices in

, .txt, and .xls formats.

1

Transceiver channels are arranged in groups of six. For GX devices, the lowest six

channels on the left side of the device are labeled GXB_L0, the next group is GXB_L1,

and so on. Channels on the right side of the device are labeled GXB_R0, GXB_R1, and

so on. Be sure to connect the Hard IP for PCI Express on the left side of the device to

appropriate channels on the left side of the device, as specified in the

Pin-out Files for

Altera Devices

.

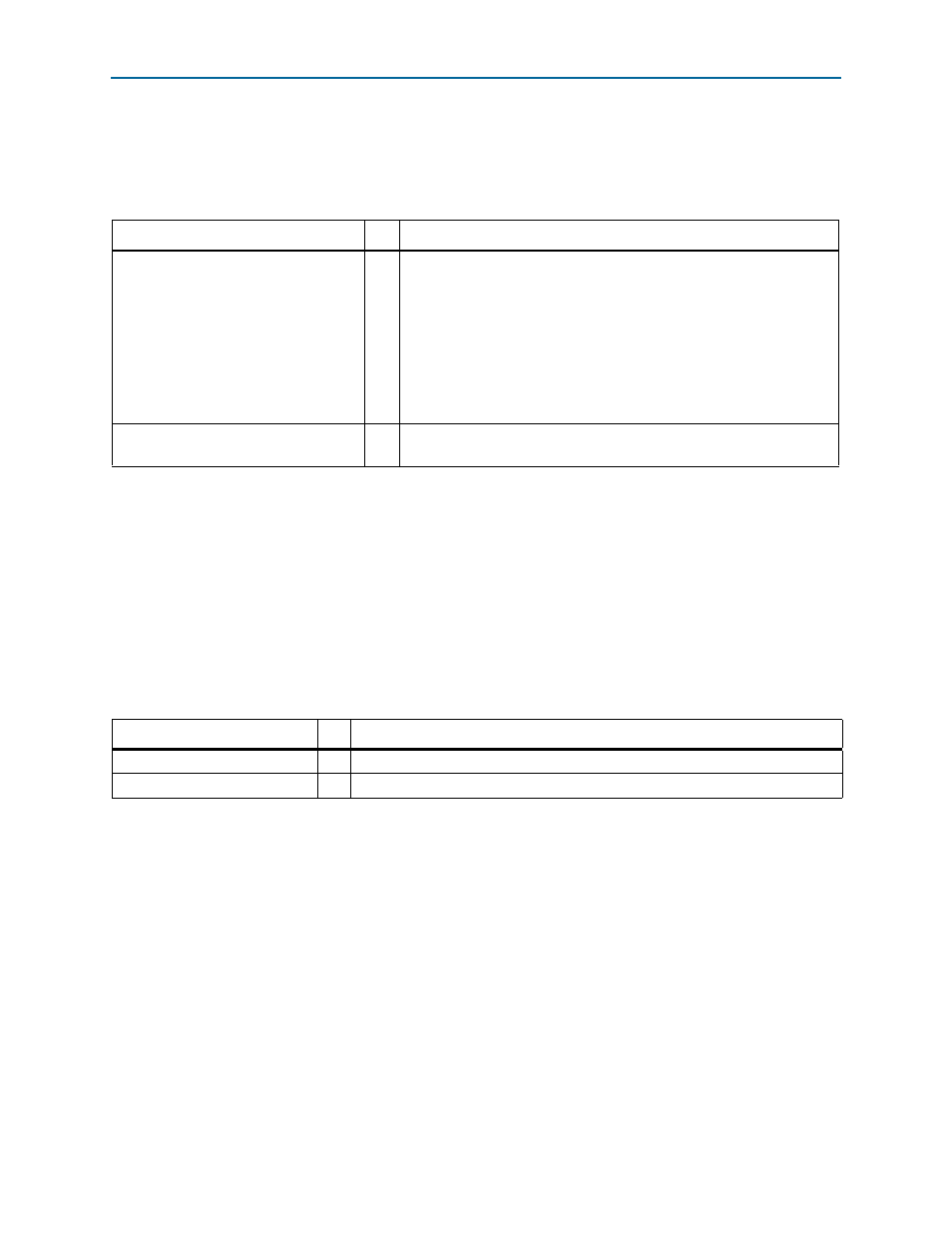

Table 7–24. Transceiver Control Signals

Signal Name

I/O

Description

reconfig_fromxcvr[(

reconfig_toxcvr[(

O

These are the parallel transceiver dynamic reconfiguration buses.

Dynamic reconfiguration is required to compensate for variations due to

process, voltage and temperature (PVT). Among the analog settings that

you can reconfigure are: V

OD

, pre-emphasis, and equalization.

You can use the Altera Transceiver Reconfiguration Controller to

dynamically reconfigure analog settings in Arria V devices. For more

information about instantiating the Altera Transceiver Reconfiguration

Controller IP core refer to

Chapter 15, Transceiver PHY IP

.

busy_xcvr_reconfig

I

When asserted, indicates that the a reconfiguration operation is in

progress.

Table 7–25. 1-Bit Interface Signals

Signal I/O

Description

tx_out

[

O

Transmit input. These signals are the serial outputs.

rx_in

I

Receive input. These signals are the serial inputs.

Note to

:

(1)