Programming model for avalon-mm root port, Programming model for avalon-mm root port –17 – Altera Arria V Hard IP for PCI Express User Manual

Page 171

Chapter 8: Register Descriptions

8–17

PCI Express Avalon-MM Bridge Control Register Access Content

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

1

The high performance TLPs implemented by Avalon-MM ports in the Avalon-MM

Bridge are also available for Root Ports. For more information about these TLPs, refer

to

Avalon-MM Bridge TLPs

.

Table 8–32

describes the Root Port TLP data registers.

Programming Model for Avalon-MM Root Port

The Application Layer writes the Root Port TLP TX Data registers with TLP formatted

data for Configuration Read and Write Requests, Message TLPs, I/O Read and Write

Requests, or single dword Memory Read and Write Requests. The Application Layer

data must be in the appropriate TLP format with the data payload aligned to the TLP

address. Aligning the payload data to the TLP address may result in the payload data

being either aligned or unaligned to the qword.

Figure 8–1

illustrates three dword

TLPs with data that is aligned and unaligned to the qword.

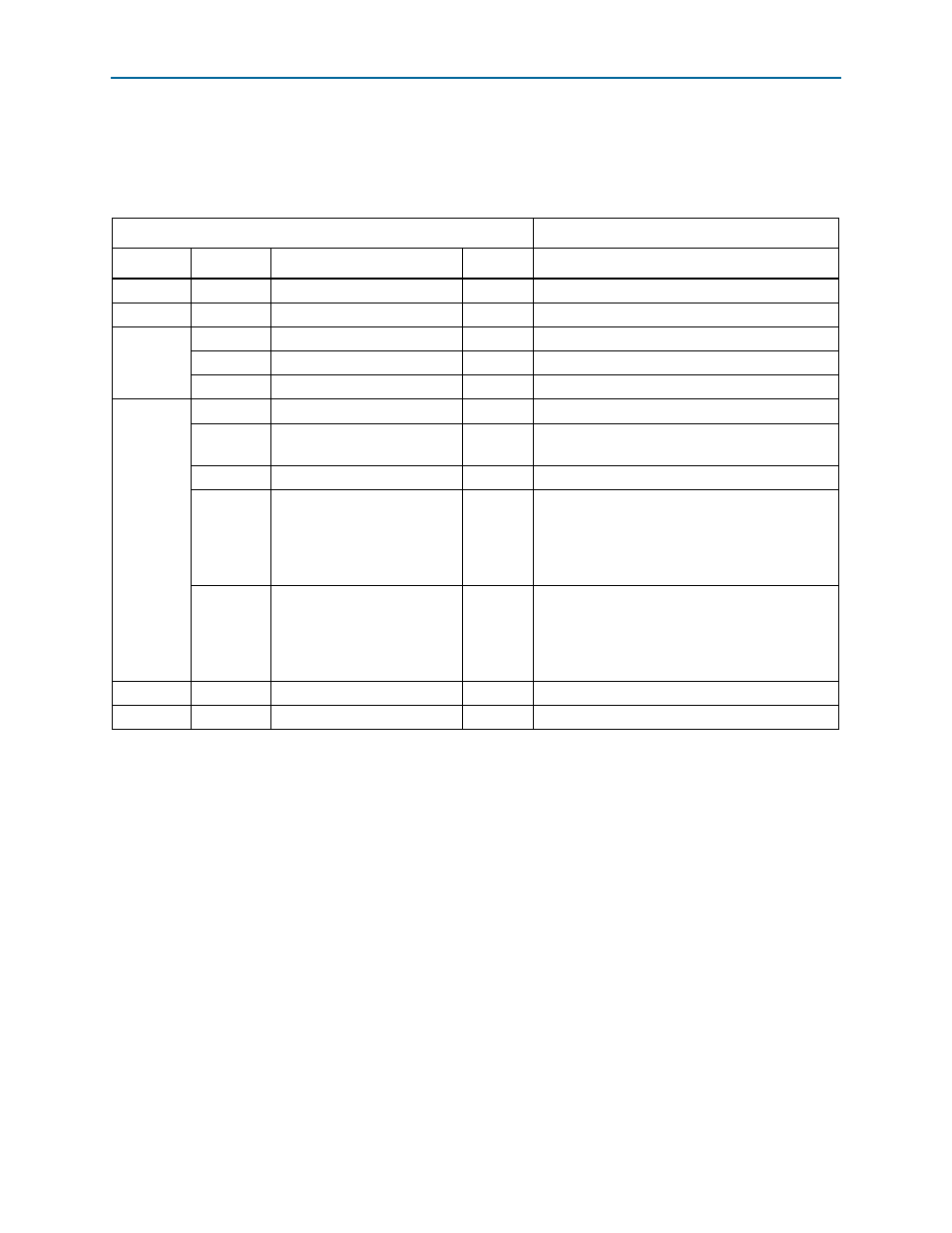

Table 8–32. Root Port TLP Data Registers

0x2000–0x2FFF

Root-Port Request Registers

Address Range: 0x2800-0x2018

Address

Bits

Name

Access

Description

0x2000

[31:0]

RP_TX_REG0

RW

Lower 32 bits of the TX TLP.

0x2004

[31:0]

RP_TX_REG1

RW

Upper 32 bits of the TX TLP.

0x2008

[31:2]

Reserved

—

—

[1]

RX_TX_CNTRL.SOP

RW

Write 1’b1 to specify the start of a packet.

[0]

RX_TX_CNTRL.EOP

RW

Write 1’b1 to specify the end of a packet.

0x2010

[31:16]

Reserved

—

—

[15:8]

RP_RXCPL_STATUS

RC

Specifies the number of words in the RX

completion FIFO contain valid data.

[7:2]

Reserved

—

—

[1]

RP_RXCPL_STATUS.SOP

RC

When 1’b1, indicates that the data for a

Completion TLP is ready to be read by the

Application Layer. The Application Layer must poll

this bit to determine when a Completion TLP is

available.

[0]

RP_RXCPL_STATUS.EOP

RC

When 1’b1, indicates that the final data for a

Completion TLP is ready to be read by the

Application Layer. The Application Layer must poll

this bit to determine when the final data for a

Completion TLP is available.

0x2014

[31:0]

RP_RXCPL_REG0

R

Lower 32 bits of a Completion TLP.

0x2018

[31:0]

RP_RXCPL_REG1

R

Upper 32 bits of a Completion TLP.