Generating the testbench, Generating the testbench –10 – Altera Arria V Hard IP for PCI Express User Manual

Page 26

2–10

Chapter 2: Getting Started with the Arria Hard IP for PCI Express

Qsys Design Flow

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

■

pcie_reconfig_driver_0—This Avalon-MM master drives the Transceiver

Reconfiguration Controller. The pcie_reconfig_driver_0 is implemented in clear

text that you can modify if your design requires different reconfiguration

functions. After you generate your Qsys system, the Verilog HDL for this

component is available as:

■

Transceiver Reconfiguration Controller—The Transceiver Reconfiguration

Controller dynamically reconfigures analog settings to improve signal quality. For

Gen1 and Gen2 data rates, the Transceiver Reconfiguration Controller must

perform offset cancellation and PLL calibration.

Generating the Testbench

Follow these steps to generate the chaining DMA testbench:

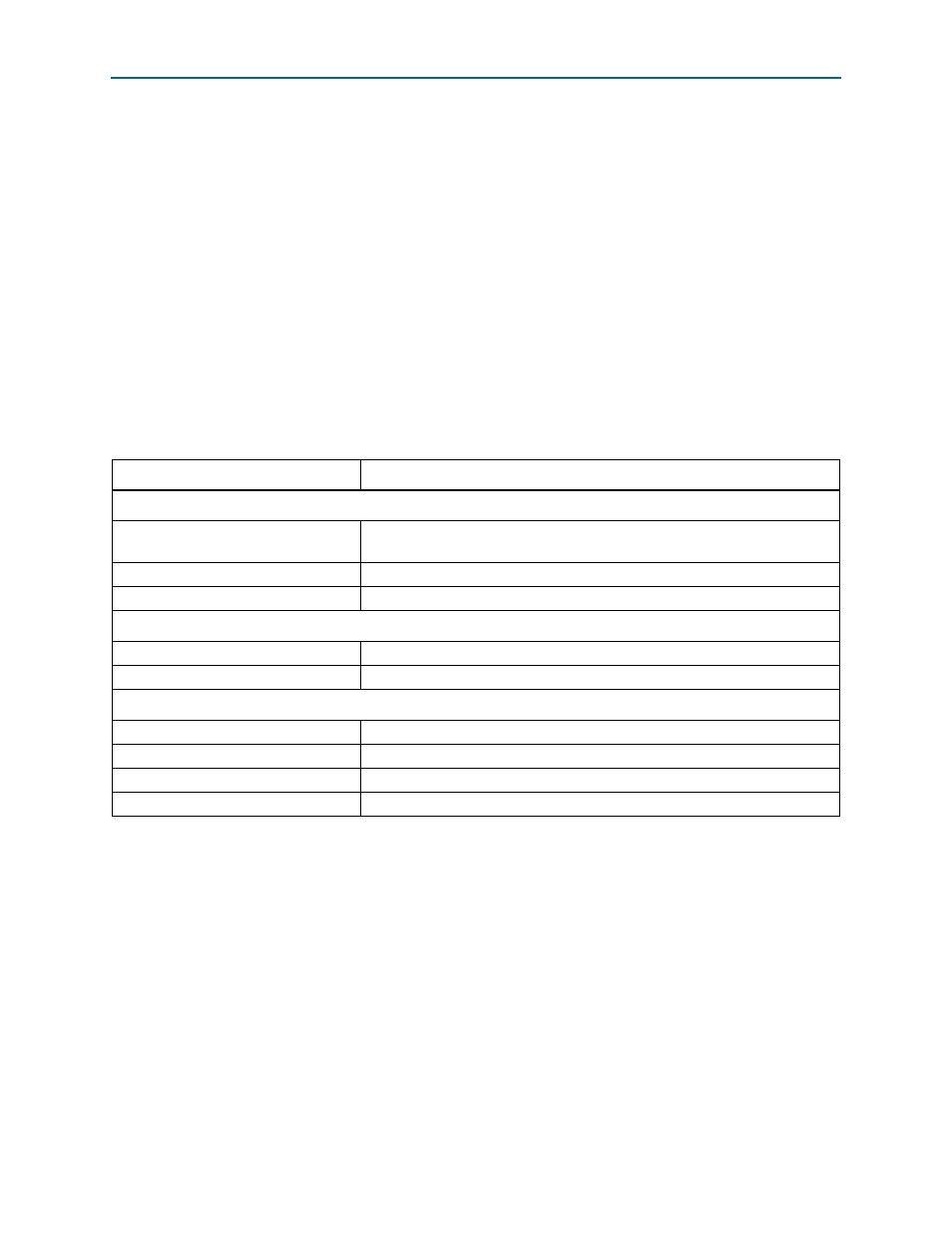

1. On the Qsys Generation tab, specify the parameters listed in the following table.

2. Click the Generate button at the bottom of the Generation tab to create the

chaining DMA testbench.

Table 2–9. Parameters to Specify on the Generation Tab in Qsys

Parameter

Value

Simulation

Create simulation model

None. (This option generates a simulation model you can include in your own

custom testbench.)

Create testbench Qsys system

Standard, BFMs for standard Avalon interfaces

Create testbench simulation model

Verilog

Synthesis

Create HDL design files for synthesis

Turn this option on

Create block symbol file (.bsf)

Turn this option on

Output Directory

Path

pcie_qsys/gen1_x4_example_design

Simulation

Leave this option blank

Testbench

(1)

pcie_qsys/gen1_x4_example_design/testbench

Synthesis

(2)

pcie_qsys/gen1_x4_example_design/synthesis

Note to

Table 2–9

:

(1) Qsys automatically creates this path by appending testbench to the output directory/.

(2) Qsys automatically creates this path by appending synthesis to the output directory/.