Altera Arria V Hard IP for PCI Express User Manual

Page 133

Chapter 7: IP Core Interfaces

7–35

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

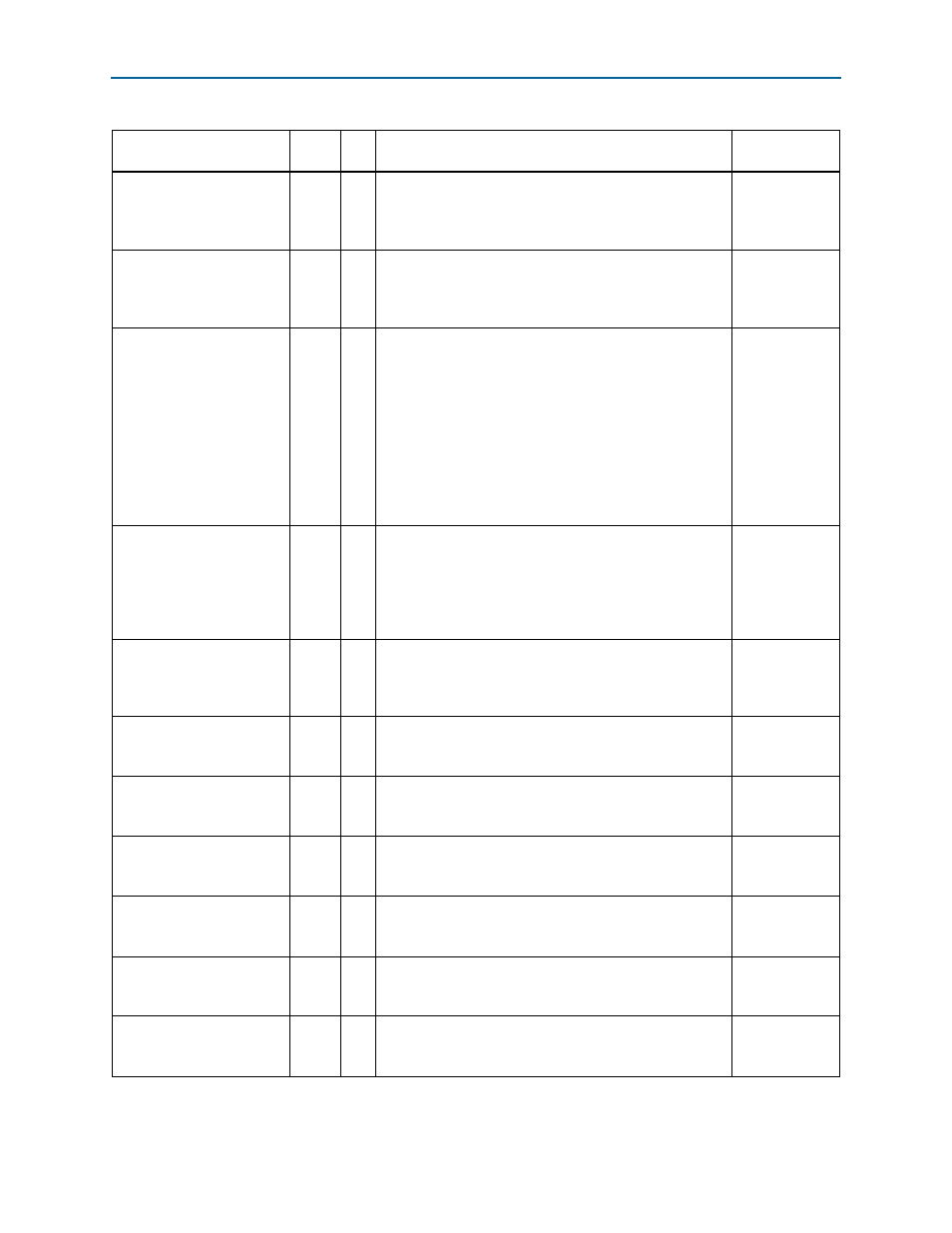

cfg_slot_ctrl

16

O

cfg_slotcsr[15:0]

is the Slot Control register of the PCI

Express capability structure. This register is only available

in Root Port mode.

Table 8–7 on

page 8–4

Table 8–8 on

page 8–4

cfg_link_ctrl

16

O

cfg_link_ctrl[15:0]

is the primary Link Control

register of the PCI Express capability structure.

Table 8–7 on

page 8–4

Table 8–8 on

page 8–4

cfg_link_ctrl2

16

O

cfg_link2csr[15:0]

is the secondary Link Control

register of the PCI Express capability structure for Gen2

operation.

When

tl_cfg_addr=2

,

tl_cfg_ctl

returns the primary

and secondary Link Control registers,

{cfg_link_ctrl[15:0], cfg_link_ctrl2[15:0]}

,

the primary Link Status register contents is available on

tl_cfg_sts[46:31]

.

For Gen1 variants, the link bandwidth notification bit is

always set to 0. For Gen2 variants, this bit is set to 1.

cfg_prm_cmd_func<n>

16

O

Base/Primary Command register for the PCI Configuration

Space.

0x004 (Type 0)

0x004 (Type 1)

cfg_root_ctrl

8

O

Root Control register of the PCI-Express capability. This

register is only available in Root Port mode.

Table 8–7 on

page 8–4

Table 8–8 on

page 8–4

cfg_sec_ctrl

16

O

Secondary bus Control register of the PCI-Express

capability. This register is only available in Root Port mode.

0x01C

cfg_secbus

8

O

Secondary bus number. Available in Root Port mode.

0x018

cfg_subbus

8

O

Subordinate bus number. Available in Root Port mode.

0x018

cfg_msi_addr[31:0]

32

O

Maps to the lower 32 bits of the MSI address of the MSI

Capability Structure.

0x050

cfg_msi_addr[63:32]

32

O

Maps to the upper 32 bits of the MSI address of the MSI

Capability Structure

0x050

cfg_io_bas

20

O

The upper 20 bits of the IO limit registers of the Type1

Configuration Space. This register is only available in Root

Port mode.

0x01C

Table 7–14. Configuration Space Register Descriptions (Part 2 of 4)

Register

Width

Dir

Description

Register

Reference