Altera Arria V Hard IP for PCI Express User Manual

Page 20

2–4

Chapter 2: Getting Started with the Arria Hard IP for PCI Express

Customizing the Endpoint in the MegaWizard Plug-In Manager Design Flow

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

1. On the Tools menu, click MegaWizard Plug-In Manager. The MegaWizard

Plug-In Manager appears.

2. Select Create a new custom megafunction variation and click Next.

3. In Which device family will you be using? Select the Arria device family.

4. Expand the Interfaces directory under Installed Plug-Ins by clicking the + icon

left of the directory name, expand PCI Express, then click Arria Hard IP for PCI

Express

5. Select the output file type for your design. This walkthrough supports VHDL and

Verilog HDL. For this example, select Verilog HDL.

6. Specify a variation name for output files <working_dir>/example_design/

<variation name>. For this walkthrough, specify

gen1_x4.

7. Click Next to open the parameter editor for the Arria Hard IP for PCI Express.

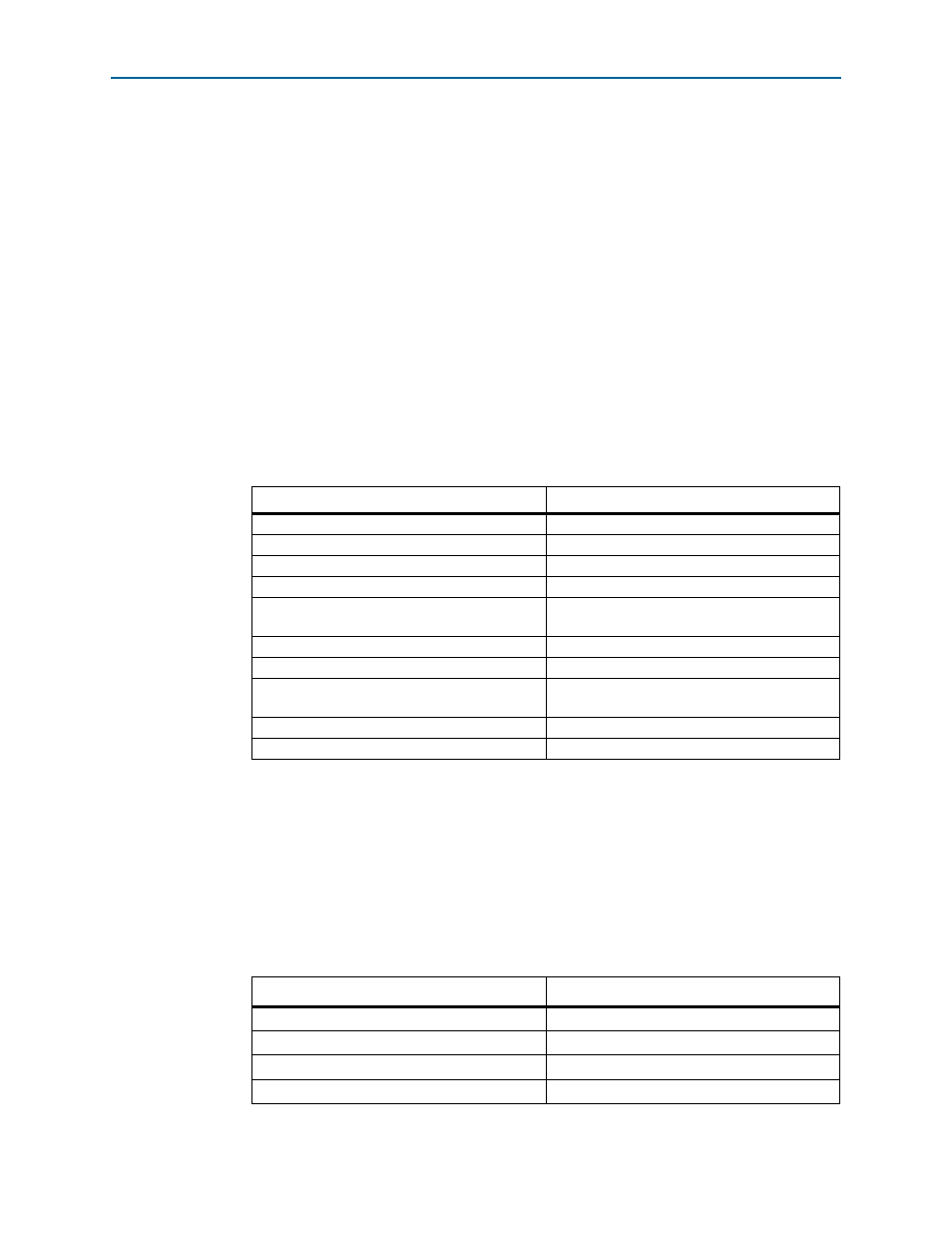

8. Specify the System Settings values listed in the following table.

1

Each function shares the parameter settings on the Device, Error Reporting, Link,

Slot

, and Power Management tabs. Each function has separate parameter settings for

the Base Address Registers, Base and Limit Registers for Root Ports, Device

Identification Registers

, and the PCI Express/PCI Capabilities parameters. When

you click on a Func

reflect the Func

9. Specify the Device parameters listed in

Table 2–2

.

Table 2–1. System Settings Parameters

Parameter

Value

Number of Lanes

x4

Lane Rate

Gen 1 (2.5 Gbps)

Port type

Native endpoint

Application Layer interface

Avalon-ST 64-bit

RX buffer credit allocation - performance for

received requests

Low

Reference clock frequency

100 MHz

Use 62.5 MHz Application Layer clock for ×1

Leave this option off

Use deprecated RX Avalon-ST data byte enable

port (rx_st_be)

Leave this option off

Enable configuration via the PCIe link

Leave this option off

Number of functions

1

Table 2–2. Device

Parameter

Value

Maximum payload size

128 bytes

Number of tags supported

32

Completion timeout range

ABCD

Implement completion timeout disable

On