Altera Arria V Hard IP for PCI Express User Manual

Page 174

8–20

Chapter 8: Register Descriptions

PCI Express Avalon-MM Bridge Control Register Access Content

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

Table 8–33

describes the

Interrupt Status

register for Root Ports. Refer to

Table 8–35

for the definition of the

Interrupt Status

register for Endpoints.

Table 8–34

describes fields of the Avalon

Interrupt Enable

register for Root Ports.

Refer to

Table 8–36

for the definition of this register for Endpoints.

PCI Express to Avalon-MM Interrupt Status and Enable Registers for

Endpoints

The registers in this section contain status of various signals in the PCI Express

Avalon-MM bridge logic and allow Avalon interrupts to be asserted when enabled. A

processor local to the interconnect fabric that processes the Avalon-MM interrupts can

access these registers.

1

These registers must not be accessed by the PCI Express Avalon-MM bridge master

ports; however, there is nothing in the hardware that prevents PCI Express

Avalon-MM bridge master port from accessing these registers.

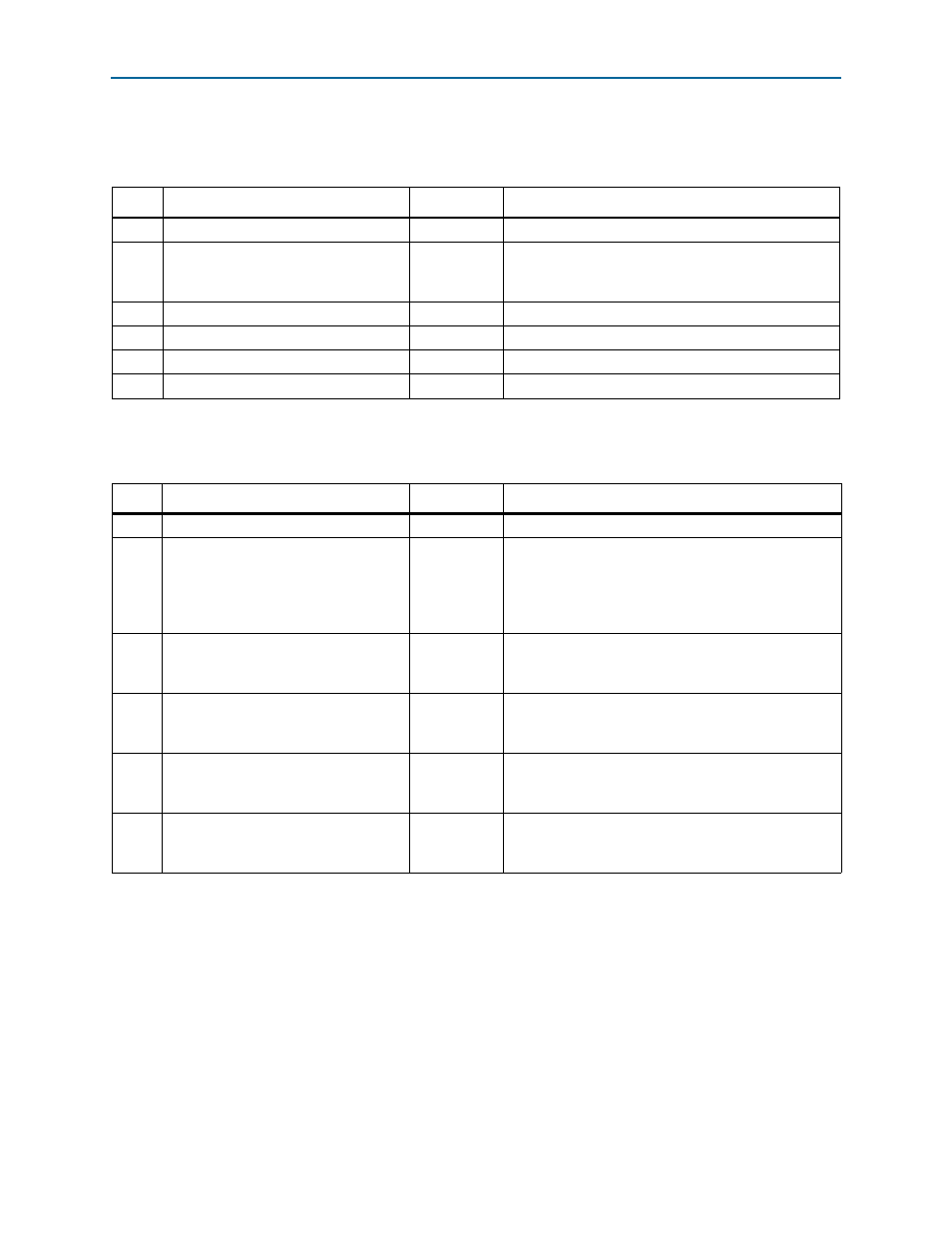

Table 8–33. Avalon-MM Interrupt Status Registers for Root Ports

0x3060

Bits

Name

Access Mode

Description

[31:5]

Reserved

—

—

[4]

RPRX_CPL_RECEIVED

RW1C

Set to 1’b1 when the Root Port has received a

Completion TLP for an outstanding Non-Posted request

from the TLP Direct channel.

[3]

INTD_RECEIVED

RW1C

The Root Port has received INTD from the Endpoint.

[2]

INTC_RECEIVED

RW1C

The Root Port has received INTC from the Endpoint.

[1]

INTB_RECEIVED

RW1C

The Root Port has received INTB from the Endpoint.

[0]

INTA_RECEIVED

RW1C

The Root Port has received INTA from the Endpoint.

Table 8–34. INT-X Interrupt Enable Register for Root Ports

0x3070

Bit

Name

Access Mode

Description

[31:5]

Reserved

—

—

[4]

RPRX_CPL_RECEIVED

RW

When set to 1’b1, enables the assertion of

CraIrq_o

when the Root Port Interrupt Status register

RPRX_CPL_RECEIVED

bit indicates it has received a

Completion for a Non-Posted request from the TLP

Direct channel.

[3]

INTD_RECEIVED_ENA

RW

When set to 1’b1, enables the assertion of

CraIrq_o

when the Root Port Interrupt Status register

INTD_RECEIVED

bit indicates it has received INTD.

[2]

INTC_RECEIVED_ENA

RW

When set to 1’b1, enables the assertion of

CraIrq_o

when the Root Port Interrupt Status register

INTC_RECEIVED

bit indicates it has received INTC.

[1]

INTB_RECEIVED_ENA

RW

When set to 1’b1, enables the assertion of

CraIrq_o

when the Root Port Interrupt Status register

INTB_RECEIVED

bit indicates it has received INTB.

[0]

INTA_RECEIVED_ENA

RW

When set to 1’b1, enables the assertion of

CraIrq_o

when the Root Port Interrupt Status register

INTA_RECEIVED

bit indicates it has received INTA.