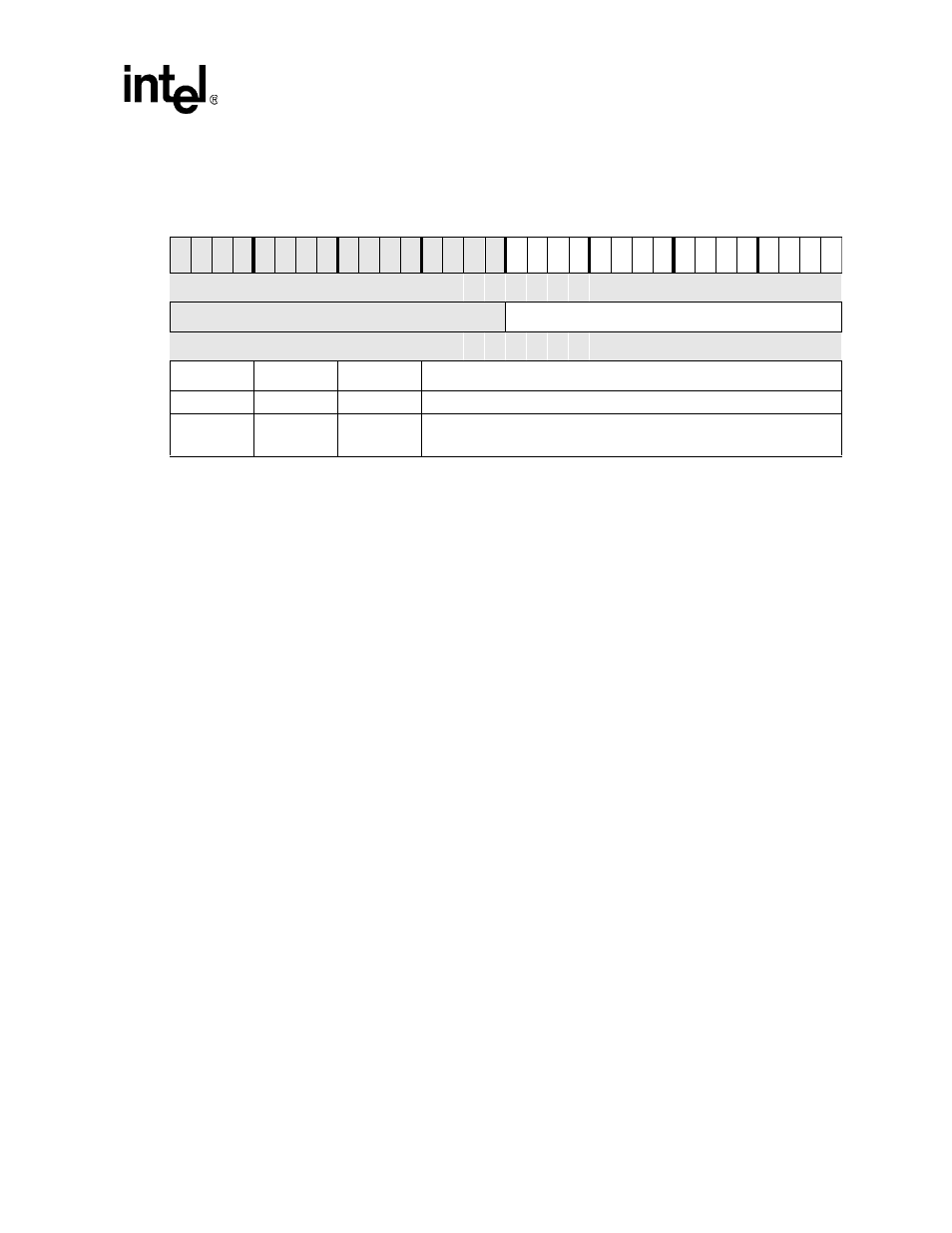

Table 17-13. acr bit definitions, 10 line control register (lcr) – Intel PXA26X User Manual

Page 605

Intel® PXA26x Processor Family Developer’s Manual

17-21

Hardware UART

17.5.10

Line Control Register (LCR)

The Line Control Register (LCR) specifies the format for the asynchronous data communications

exchange. The serial data format consists of a start bit, five to eight data bits, an optional parity bit,

and one, one and a half, or two stop bits. The LCR has bits that allow access to the Divisor Latch

and bits that can cause a break condition. The LCR bit definitions are shown in

Table 17-13.

ACR

Bit Definitions

Physical Address

0x4160_002C

Autobaud Count Reg. (ACR)

PXA26x Processor Family Hardware

UART

User

Settings

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Reserved

Count Value

Reset

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Access

Name

Description

31:16

N/A

—

Reserved – Read as unknown and must be written as zero.

15:0

R

ACR[15:0]

AUTO-BAUD COUNT REGISTER BITS 15 – 0:

Number of 14.7456-MHz-clock cycles within a start bit pulse