8 codec access register (car), Table 13-14. codec access register, 9 pcm data register (pcdr) – Intel PXA26X User Manual

Page 488: Table 13-15. pcm data register, Table 13-14, “codec access, Register

13-26

Intel® PXA26x Processor Family Developer’s Manual

AC97 Controller Unit

13.8.3.8

Codec Access Register (CAR)

13.8.3.9

PCM Data Register (PCDR)

Writing a 32-bit sample to this register updates the data into the PCM transmit FIFO. Reading this

register gets a 32-bit sample from the PCM receive FIFO.

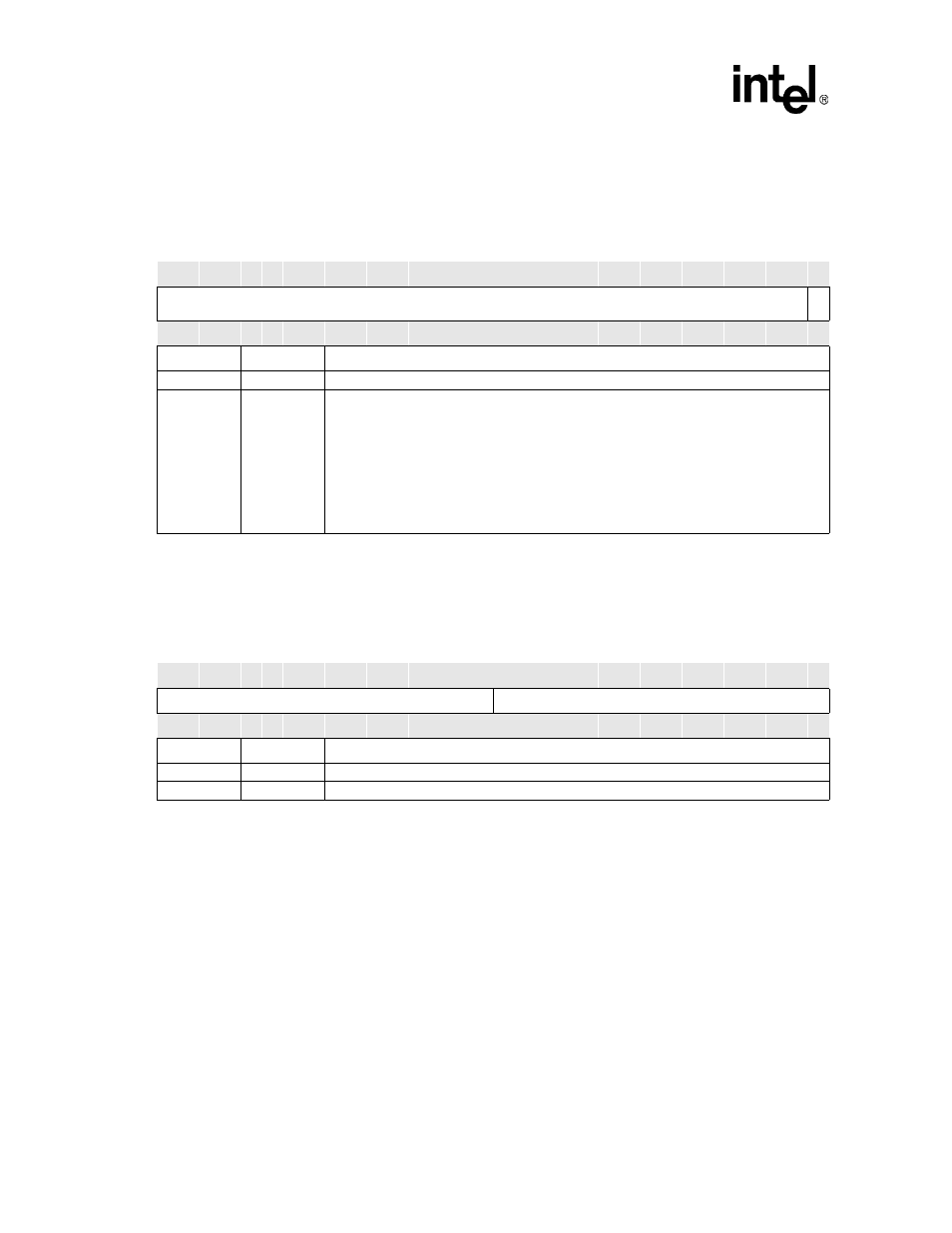

Table 13-14. Codec Access Register

Physical Address

4050_0020

CAR Register

AC97

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Reserved

CAI

P

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

31:1

—

Reserved

0

CAIP

CODEC ACCESS IN PROGRESS (CAIP):

This bit is read by software to check whether a codec I/O cycle is currently in progress.

0 – No cycle is in progress and the act of reading the register sets this bit to ‘1’. This

reserves the right for the software driver to perform the I/O cycle. Once the cycle is

complete, this bit is automatically cleared. Software can clear this bit by writing a ‘0’ to

this bit location if it decides not to perform a codec I/O cycle after having read this bit.

1 – Indicates that another driver is performing a codec I/O cycle across the AC-link and the

currently accessing driver must try again later. (This bit applies to all codec I/O cycles -

GPIO or otherwise).

Table 13-15. PCM Data Register

Physical Address

4050_0040

PCDR Register

AC97

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

PCM_RDATA

PCM_LDATA

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

31:16

PCM_RDATA PCM right-channel data

15:0

PCM_LDATA PCM left-channel data