3 global status register (gsr), Table 13-9. global status register (sheet 1 of 2), Table 13-9, “global status register – Intel PXA26X User Manual

Page 484

13-22

Intel® PXA26x Processor Family Developer’s Manual

AC97 Controller Unit

13.8.3.3

Global Status Register (GSR)

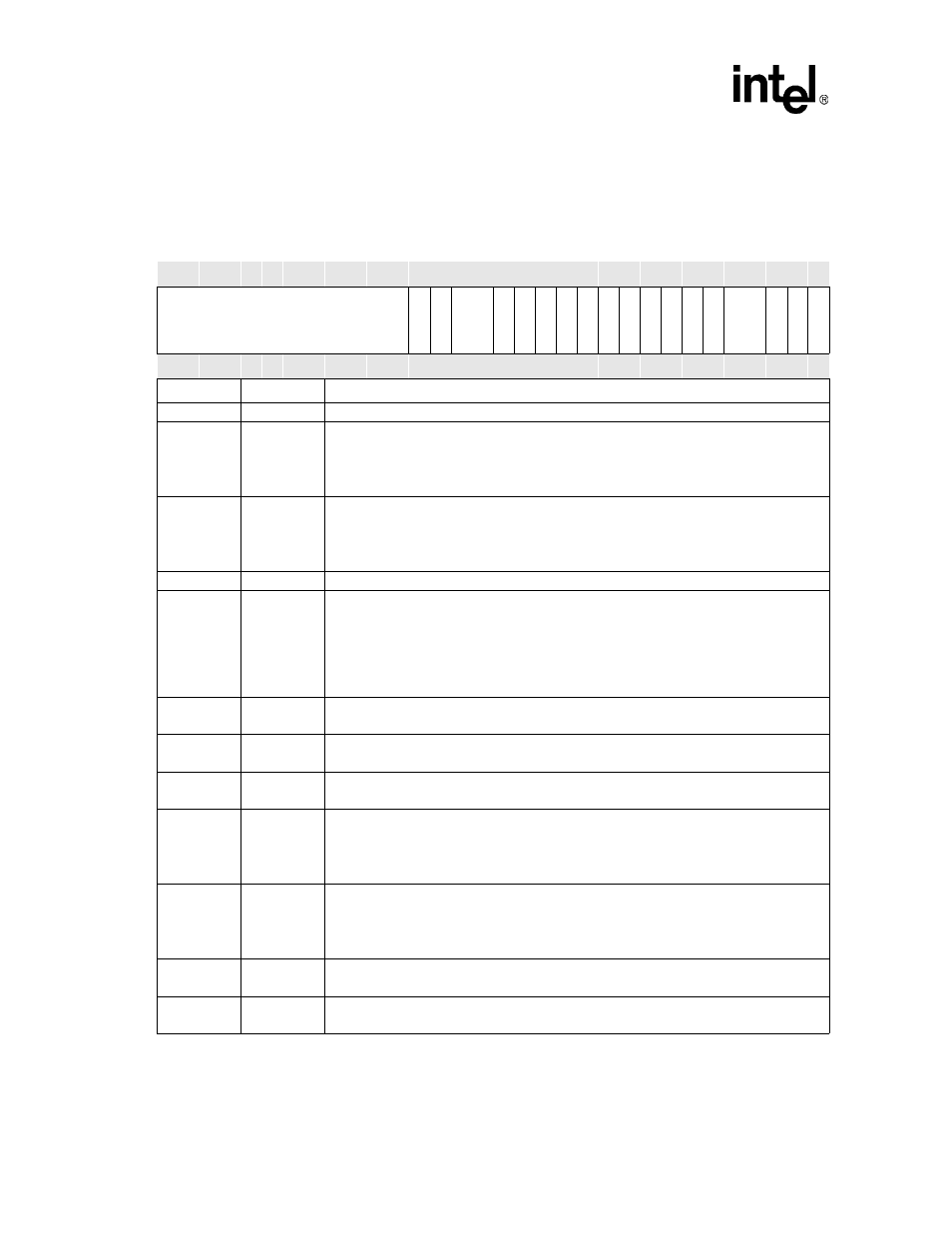

Table 13-9. Global Status Register (Sheet 1 of 2)

Physical Address

4050_001C

GSR Register

AC97

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Reserved

CD

ON

E

SDO

N

E

R

e

ser

ve

d

RD

CS

B

IT3SL

T12

B

IT2SL

T12

B

IT1SL

T12

SEC

RE

S

PR

IR

E

S

SC

R

PC

R

MI

N

T

PO

INT

P

IIN

T

R

e

ser

ve

d

MOI

N

T

M

IIN

T

GS

CI

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

31:20

—

Reserved

19

CDONE

COMMAND DONE (CDONE):

0 – ACUNIT has not sent command address and data to the codec.

1 – ACUNIT has sent command address and data to the codec.

This bit is cleared by software writing a ‘1’ to this location (interruptible)

18

SDONE

STATUS DONE (SDONE):

0 – ACUNIT has not received status address and data from the codec.

1 – ACUNIT has received status address and data from the codec.

This bit is cleared by software writing a ‘1’ to this location (interruptible)

17:16

—

Reserved

15

RDCS

READ COMPLETION STATUS:

This bit indicates the status of codec read completions.

0 – The codec read completed normally

1 – The codec read resulted in a timeout.

The bit remains set until cleared by software. This bit is cleared by software writing a ‘1’ to

this location.

14

BIT3SLT12

BIT 3 OF SLOT 12:

Display Bit 3 of the most recent valid slot 12

13

BIT2SLT12

BIT 2 OF SLOT 12:

Display Bit 2 of the most recent valid slot 12

12

BIT1SLT12

BIT 1 OF SLOT 12:

Display Bit 1 of the most recent valid slot 12

11

SECRES

SECONDARY RESUME INTERRUPT:

0 – A resume event has not occurred on the SDATA_IN_1.

1 – A resume event occurred on the SDATA_IN_1.

This bit is cleared by software writing a ‘1’ to this location (interruptible).

10

PRIRES

PRIMARY RESUME INTERRUPT:

0 – A resume event has not occurred on the SDATA_IN_0.

1 – A resume event occurred on the SDATA_IN_0.

This bit is cleared by software writing a ‘1’ to this location (interruptible).

9

SCR

SECONDARY CODEC READY (SCR):

Reflects the state of the codec ready bit in SDATA_IN_1 (interruptible)

8

PCR

PRIMARY CODEC READY (PCR):

Reflects the state of the codec ready bit in SDATA_IN_0 (interruptible)