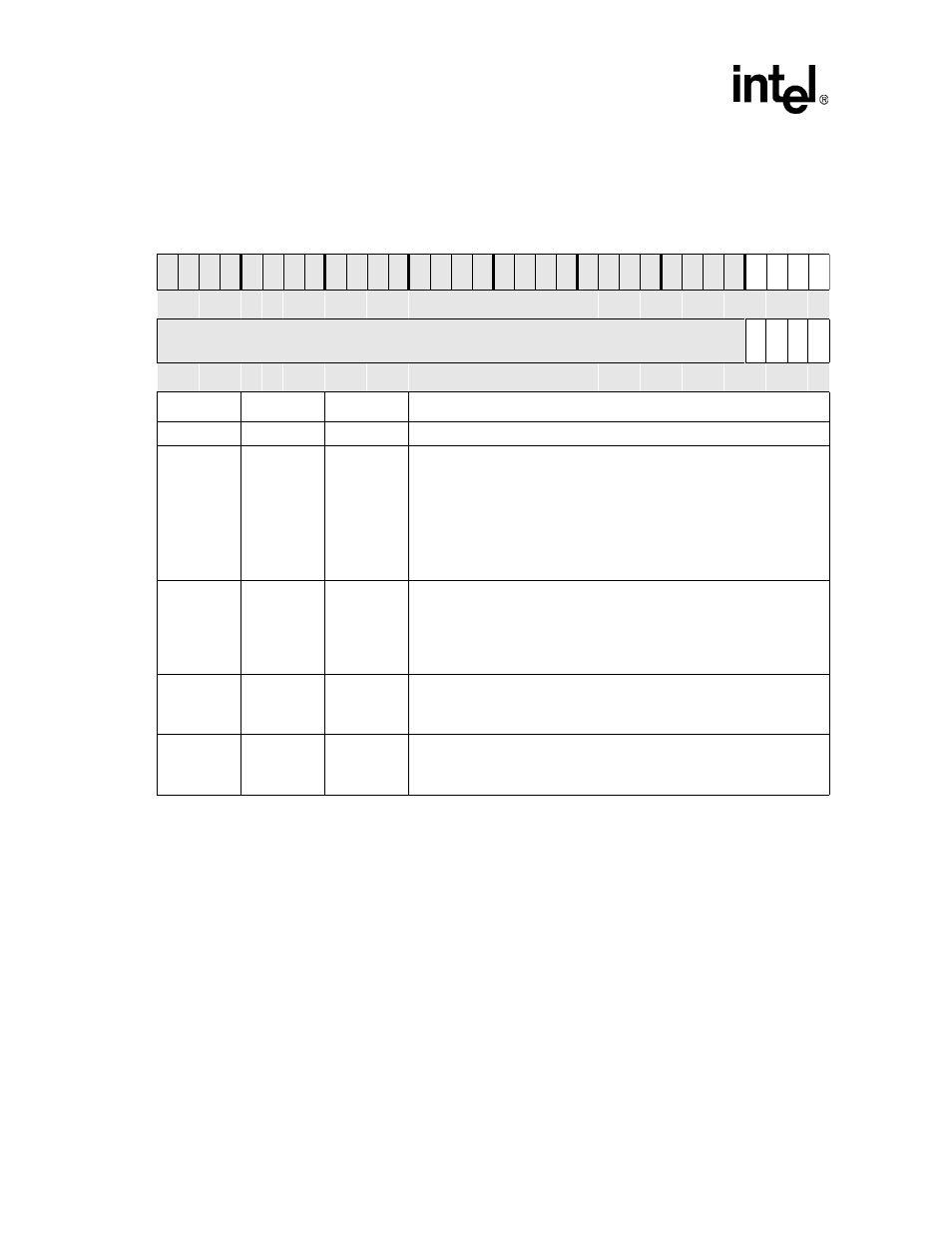

Table 17-12. abr bit definitions, 9 auto-baud count register (acr) – Intel PXA26X User Manual

Page 604

17-20

Intel® PXA26x Processor Family Developer’s Manual

Hardware UART

Note:

Auto-baud rate detection is not supported with slow infrared Mode.

See

Section 17.4.4, “Auto-Baud-Rate Detection”

for more information on auto-baud rate.

17.5.9

Auto-Baud Count Register (ACR)

The ACR stores the number of 14.7456-MHz-clock cycles within a start bit pulse. This value is

then used by the processor or the UART to calculate the baud rate. If auto-baud mode (ABR[ABE])

and auto-baud interrupts (ABR[ABLIE]) are enabled, the UART interrupts the processor with the

auto-baud lock interrupt (IIR[ABL]) after it has written the count value into the ACR. The value is

written regardless of the state of the auto-baud UART program bit (ABR[ABUP]). The ACR bit

definitions are shown in

.

Table 17-12.

ABR Bit Definitions

Physical Address

0x4160_0028

Autobaud Control Reg. (ABR)

PXA26x processor family Hardware

UART

User

Settings

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Reserved

AB

T

AB

UP

AB

L

IE

AB

E

Reset

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

0

0

0

0

Bits

Access

Name

Description

31:4

N/A

—

Reserved – Read as unknown and must be written as zero.

3

R/W

ABT

AUTOBAUD TABLE:

Uses a table to select low-speed baud rates instead of a formula. Only valid

if ABR[ABUP] is set.

0 – Table used to calculate baud rates which limits UART to choosing

common baud rates as shown in

Section 17.4.4, “Auto-Baud-Rate

1 – Formula used to calculate baud rates allowing all possible baud rates

to be chosen by UART.

2

R/W

ABUP

AUTOBAUD UART PROGRAM:

Controls if the UART automatically programs DLL and DLH or if the

processor must program DLL and DLH based on the results in the ACR.

0 – Processor Programs Divisor Latch registers

1 – UART Programs Divisor Latch registers

1

R/W

ABLIE

AUTOBAUD LOCK INTERRUPT ENABLE:

0 – Autobaud Lock Interrupt disabled (Source IIR[ABL])

1 – Autobaud Lock Interrupt enabled (Source IIR[ABL])

0

R/W

ABE

AUTOBAUD ENABLE:

0 – Autobaud Disabled

1 – Autobaud Enabled