Table 12-22. udc status / interrupt register 1, 12 udc frame number high register (ufnhr), 1 udc frame number msb (fnmsb) – Intel PXA26X User Manual

Page 453: 2 isochronous packet error endpoint 4 (ipe4)

Intel® PXA26x Processor Family Developer’s Manual

12-43

Universal Serial Bus Device Controller

12.6.12

UDC Frame Number High Register (UFNHR)

The UDC frame number high register holds the three most significant bits of the frame number

contained in the last received SOF packet, the isochronous OUT endpoint error status, and the SOF

interrupt status/interrupt mask bit.

12.6.12.1

UDC Frame Number MSB (FNMSB)

The UFNHR[FNMSB] is the three most significant bits of the 11-bit frame number contained in

the last received SOF packet. The remaining bits are located in the UFNLR. This information is

used for isochronous transfers. These bits are updated every SOF.

12.6.12.2

Isochronous Packet Error Endpoint 4 (IPE4)

The isochronous packet error for Endpoint 4 is set if Endpoint 4 is loaded with a data packet that is

corrupted. This status bit is used in the interrupt generation of endpoint 4. To maintain

synchronization, the software must monitor this bit when it services an SOF interrupt and reads the

frame number. This bit is not set if the token packet is corrupted or if the sync or PID fields of the

data packet are corrupted.

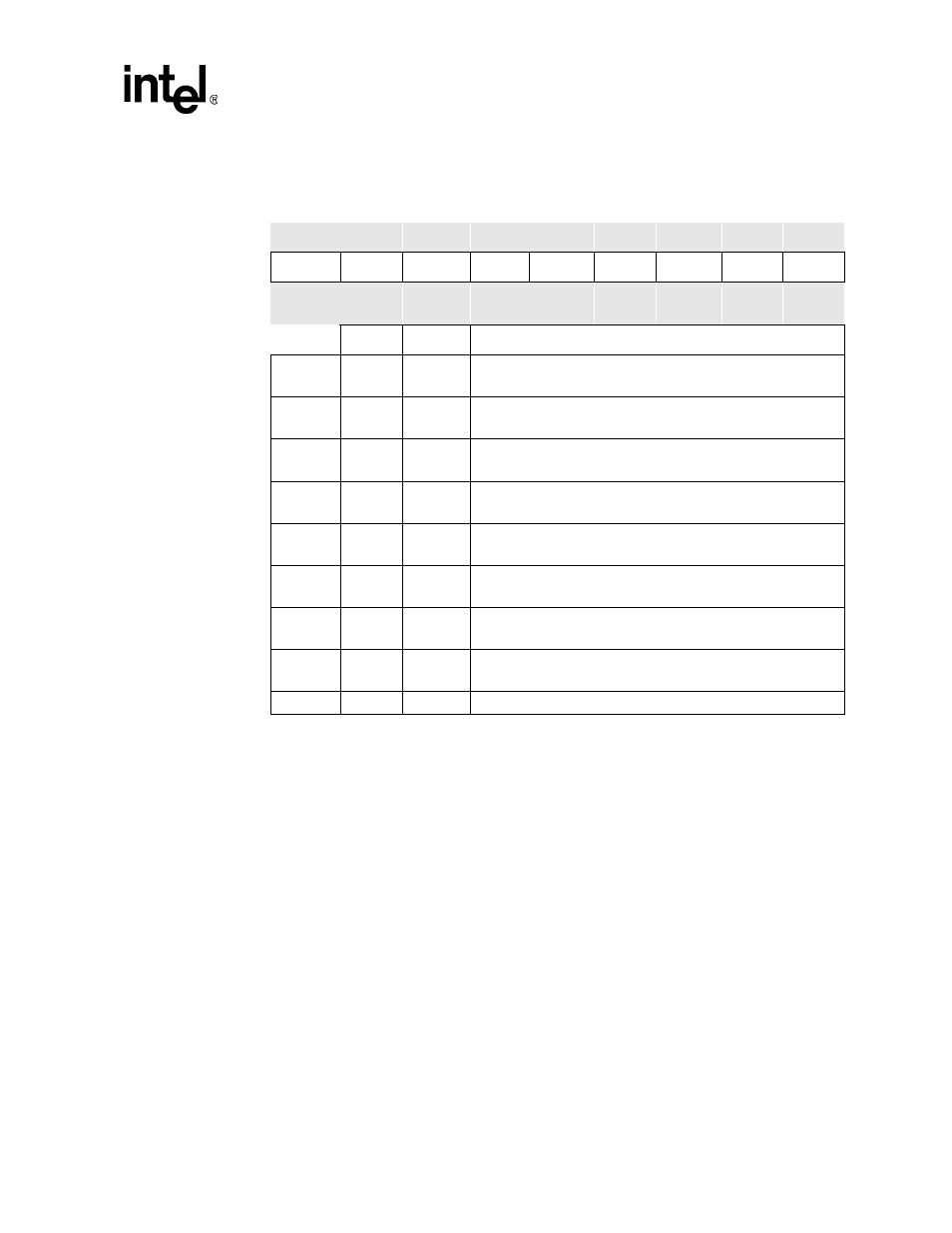

Table 12-22. UDC Status / Interrupt Register 1

0h 4060 005C

USIR1

Read/Write and Read-Only

Bit

31:8

7

6

5

4

3

2

1

0

Reserved

IR15

IR14

IR13

IR12

IR11

IR10

IR9

IR8

Rese

t

X

0

0

0

0

0

0

0

0

Bits

Name

Description

0

IR8

INTERRUPT REQUEST ENDPOINT 8 (read/write 1 to clear):

1 – Endpoint 8 needs service.

1

IR9

INTERRUPT REQUEST ENDPOINT 9 (read/write 1 to clear):

1 – Endpoint 9needs service.

2

IR10

INTERRUPT REQUEST ENDPOINT 10 (read/write 1 to clear):

1 – Endpoint 10 needs service.

3

IR11

INTERRUPT REQUEST ENDPOINT 11 (read/write 1 to clear):

1 – Endpoint 11 needs service.

4

IR12

INTERRUPT REQUEST ENDPOINT 12 (read/write 1 to clear):

1 – Endpoint 12 needs service.

5

IR13

INTERRUPT REQUEST ENDPOINT 13 (read/write 1 to clear):

1 – Endpoint 13 needs service.

6

IR14

INTERRUPT REQUEST ENDPOINT 14 (read/write 1 to clear):

1 – Endpoint 14 needs service.

7

IR15

INTERRUPT REQUEST ENDPOINT 15 (read/write 1 to clear):

1 – Endpoint 15 needs service.

31:8

—

Reserved for future use