Table 4-22. gedr1 bit definitions, Table 4-23. gedr2 register bitmap, 6 gpio alternate function register (gafr) – Intel PXA26X User Manual

Page 125: Table 4-23

Intel® PXA26x Processor Family Developer’s Manual

4-17

System Integration Unit

4.1.3.6

GPIO Alternate Function Register (GAFR)

The GPIO alternate function registers (GAFR2, GAFR1, GAFR0) contain select bits that

correspond to the 90 GPIO pins. Each GPIO can be configured to be either a generic GPIO pin, one

of 3 alternate input functions, or one of 3 alternate output functions. To select any of the alternate

input functions, the GPDR register must configure the GPIO to be an input. Similarly, only GPIOs

configured as outputs by the GPDR can be configured for alternate output functions. Each GPIO

pin has a pair of bits assigned to it whose values determine which function (normal GPIO, alternate

function 1, alternate function 2 or alternate function 3) the GPIO performs. The function selected is

determined by writing the GAFR bit pair as below:

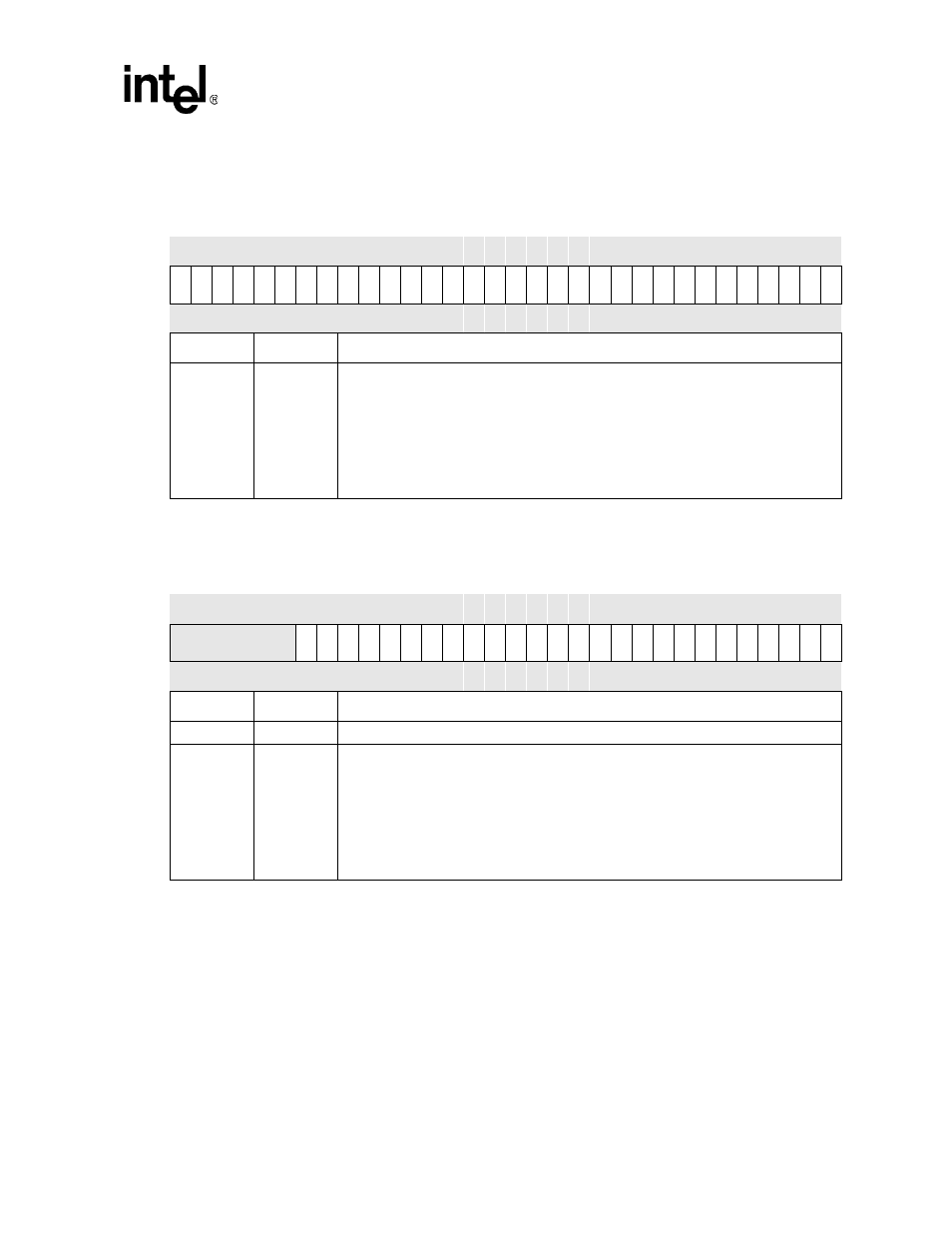

Table 4-22. GEDR1 Bit Definitions

Physical Address

0x40E0_004C

GEDR1

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

ED

6

3

ED

6

2

ED

6

1

ED

6

0

ED

5

9

ED

5

8

ED

5

7

ED

5

6

ED

5

5

ED

5

4

ED

5

3

ED

5

2

ED

5

1

ED

5

0

ED

4

9

ED

4

8

ED

4

7

ED

4

6

ED

4

5

ED

4

4

ED

4

3

ED

4

2

ED

4

1

ED

4

0

ED

3

9

ED

3

8

ED

3

7

ED

3

6

ED

3

5

ED

3

4

ED

3

3

ED

3

2

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

<31:0>

ED[x]

GPIO PIN ‘X’ EDGE DETECT STATUS (where x = 32 through 63):

READ

0 – No edge detect has occurred on pin as specified in GRER or GFER.

1 – Edge detect has occurred on pin as specified in GRER or GFER.

WRITE

0 – No effect.

1 – Clear edge detect status field.

Table 4-23. GEDR2 Register Bitmap

Physical Address

0x40E0_0050

GPIO Edge Detect Status

Register2 (GEDR2)

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Reserved

ED

8

9

ED

8

8

ED

8

7

ED

8

6

ED

8

5

ED

8

4

ED

8

3

ED

8

2

ED

8

1

ED

8

0

ED

7

9

ED

7

8

ED

7

7

ED

7

6

ED

7

5

ED

7

4

ED

7

3

ED

7

2

ED

7

1

ED

7

0

ED

6

9

ED

6

8

ED

6

7

ED

6

6

ED

6

5

ED

6

4

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

<31:26>

—

Reserved

<25:0>

ED[x]

GPIO PIN ‘X’ EDGE DETECT STATUS (where x = 64 through 89):

READ

0 – No edge detect has occurred on pin as specified in GRER or GFER.

1 – Edge detect has occurred on pin as specified in GRER or GFER.

WRITE

0 – No effect.

1 – Clear edge detect status field.