Figure 5-1. dmac block diagram, 1 direct memory access controller channels, Figure 5-1 – Intel PXA26X User Manual

Page 160

5-2

Intel® PXA26x Processor Family Developer’s Manual

Direct Memory Access Controller

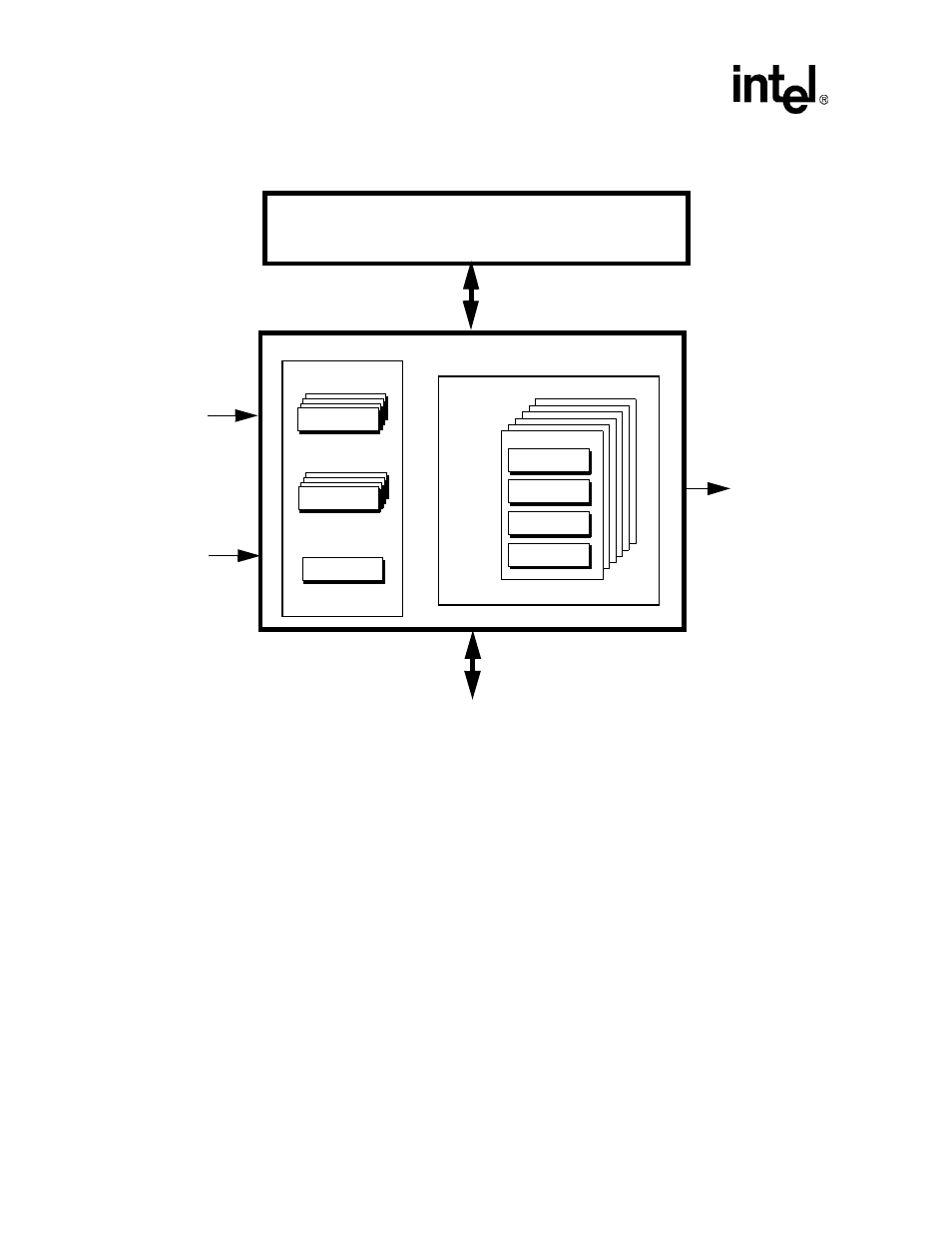

Figure 5-1. DMAC Block Diagram

5.1.1

Direct Memory Access Controller Channels

The DMAC has 16 channels, each controlled by four 32-bit registers. Each channel can be

configured to service any internal peripheral or one of the external peripherals for flow-through

transfers. Each channel is serviced in increments of the peripheral device’s burst size and is

delivered in the granularity appropriate to that device’s port width. The burst size and port width

for each device is programmed in the channel registers and is based on the device’s FIFO depth and

bandwidth needs. Due to performance issues, it is highly recommended that the user set the burst

size equal to the FIFO DMA interrupt trigger level, also called the FIFO threshold level. When

multiple channels are actively executing, the DMAC services each channel is serviced with a burst

of data. After the data burst is sent, the DMAC may perform a context switch to another active

channel. The DMAC performs context switches based on a channel’s activity, whether its target

device is currently requesting service, and where that channel lies in the priority scheme.

DDADR0

DSADR0

DTADR0

DCMD0

Channel 0

Channel 15

16 DMA Channels

DRCMR0

Control Registers

System Bus (internal)

Peripheral Bus

DREQ[1:0]

PREQ[37:0]

DMA_IRQ

DMA Controller

DINT

DCSR0

(external)

(internal)

(internal)

(internal)

Memory Controller