Table 6-1. device transactions, 1 reads and writes, 2 aborts and nonexistent memory – Intel PXA26X User Manual

Page 197

Intel® PXA26x Processor Family Developer’s Manual

6-7

Memory Controller

lists all the transactions that the processor can generate. No burst can cross an aligned 32-

byte boundary. On a 16-bit data bus, each full word access becomes a two half-word burst, with

address bit 1 set to a 0. Each write access to flash memory space must take place in one non-burst

operation, regardless of the bus size.

6.4.1

Reads and Writes

DQM[3:0] are data masking bits. When asserted (high), the corresponding bit masks the associated

byte of data on the MD[31:0] bus. When deasserted (low), the corresponding bit does not mask the

associated byte of data on the MD[31:0] bus.

•

DQM[3] corresponds to MD[31:24]

•

DQM[2] corresponds to MD[23:16]

•

DQM[1] corresponds to MD[15:8]

•

DQM[0] corresponds to MD[7:0]

For writes to SDRAM, SRAM, or Variable Latency I/O memory spaces, the DQM[3:0] lines

enable the corresponding byte of the data bus. Flash memory space stores must be exactly the

width of the flash data bus, either 16- or 32-bits. See

Section 6.8.6, “FLASH Memory Interface”

for more information.

For reads to all memory types, the DQM[3:0] lines are deasserted (set low so data is not masked)

unless SA1111CR[SA1111_x] is set for that chip select. If SA1111CR[SA1111_x] is set, then only

the appropriate byte-selects are used for the bytes being requested.

6.4.2

Aborts and Nonexistent Memory

Accessing reserved portions of the memory map results in a data abort exception.

Hardware does not detect reads and writes from or to enabled and nonexistent memory. If memory

in an enabled partition is not present, a read returns indeterminate data.

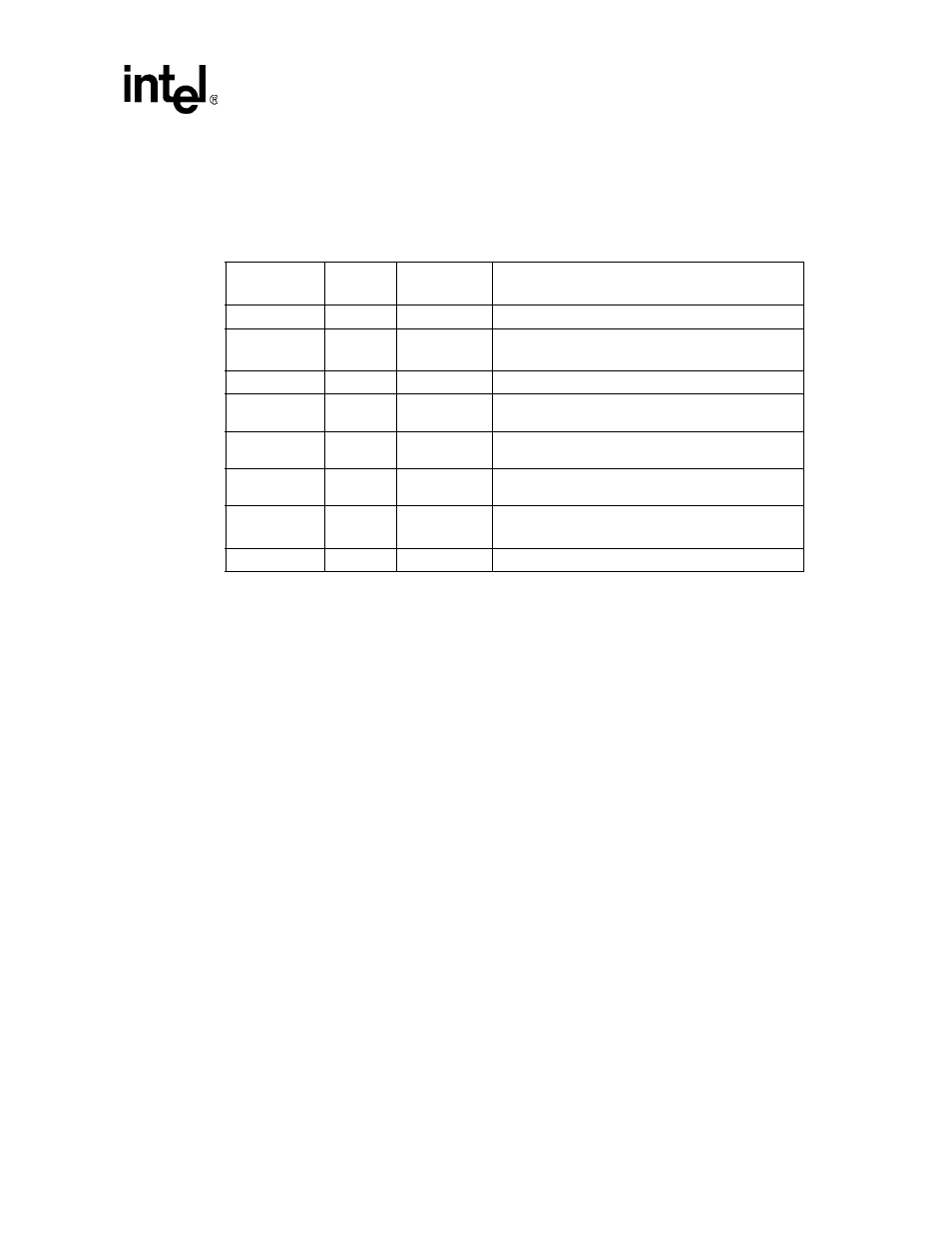

Table 6-1. Device Transactions

Bus Operation

Burst Size

(Words)

Start Address

Bits [4:2]

Description

Read single

1

Any

Generated by core, DMA, or LCD request.

Read burst

4

0

4

Generated by DMA or LCD request.

Read burst

8

0

Generated by cache line fills.

Write single

1

Any

1..4 bytes are written as specified by the byte mask.

Generated by DMA request.

Write burst

2

0,1,2

4,5,6

All 4 bytes of each word are written. Generated by DMA

request.

Write burst

3

0,1

4,5

All 4 bytes of each word are written. Generated by DMA

request.

Write burst

4

0

4

All 4 bytes of each word are written. Generated by DMA

request.

Write burst

8

0

Cacheline copyback. All 32 bytes are written.