Table 4-51. pwm_dutyn bit definitions, 3 pwm period control register (pwm_pervaln), 3 pwm period control register (pwm_perval n ) – Intel PXA26X User Manual

Page 154

4-46

Intel® PXA26x Processor Family Developer’s Manual

System Integration Unit

The FDCYCLE bit determines whether or not PWM_OUTn is a function of the DCYCLE bits in

the PWM_DUTYn register or is set high. When the FDCYCLE bit is cleared low (normal

operation), the output waveform of PWM_OUTn is cyclic, with PWM_OUTn being high for the

number of PSCLK_PWMn periods equal to DCYCLE.

If FDCYCLE = 0x0 and DCYCLE = 0x0, PWM_OUTn is set low and does not toggle.

Note:

If FDCYCLE is 0b1, PWM_OUTn is high for the entire period and is not influenced by the value

programmed in the DCYCLE bits.

shows the bitmap of the PWM Duty registers.

4.5.2.3

PWM Period Control Register (PWM_PERVALn)

The PWM Period Control register (PWM_PERVALn) contains a 10 bit field called PV. This field

determines the period of the PWM_OUTn waveform in terms of the PSCLK_PWMn clock. If this

field is cleared to zero PWMn is effectively turned off and PWM_OUTn remains in a high state.

For any non-zero value written to the PV field, the output frequency of PWMn is the frequency of

the PSCLK_OUTn divided by the value of (PV + 1). The range of the clock gate extends from a

pass-through of the PSCLK_PWMn to a clock delay of 2

6

or 64 input clocks per output pulse.

When the value of the 10 bit up-counter equals the value of (PV +1), the up-counter and the flip-

flop are reset and the values of PWM_CTRLn, PWM_PERVALn and PWM_DUTYn are loaded

into the internal versions of these registers. Resetting this flip-flop causes PWM_OUTn to go low

and the PWM cycle to start again.

Writing all zeroes to this register results in the output maintaining a high state unless

FDCYCLE = 0x0 and DCYCLE = 0x0. If FDCYCLE = 0x0 and DCYCLE = 0x0, the output

maintains a low state regardless of the value in the PV bit field.

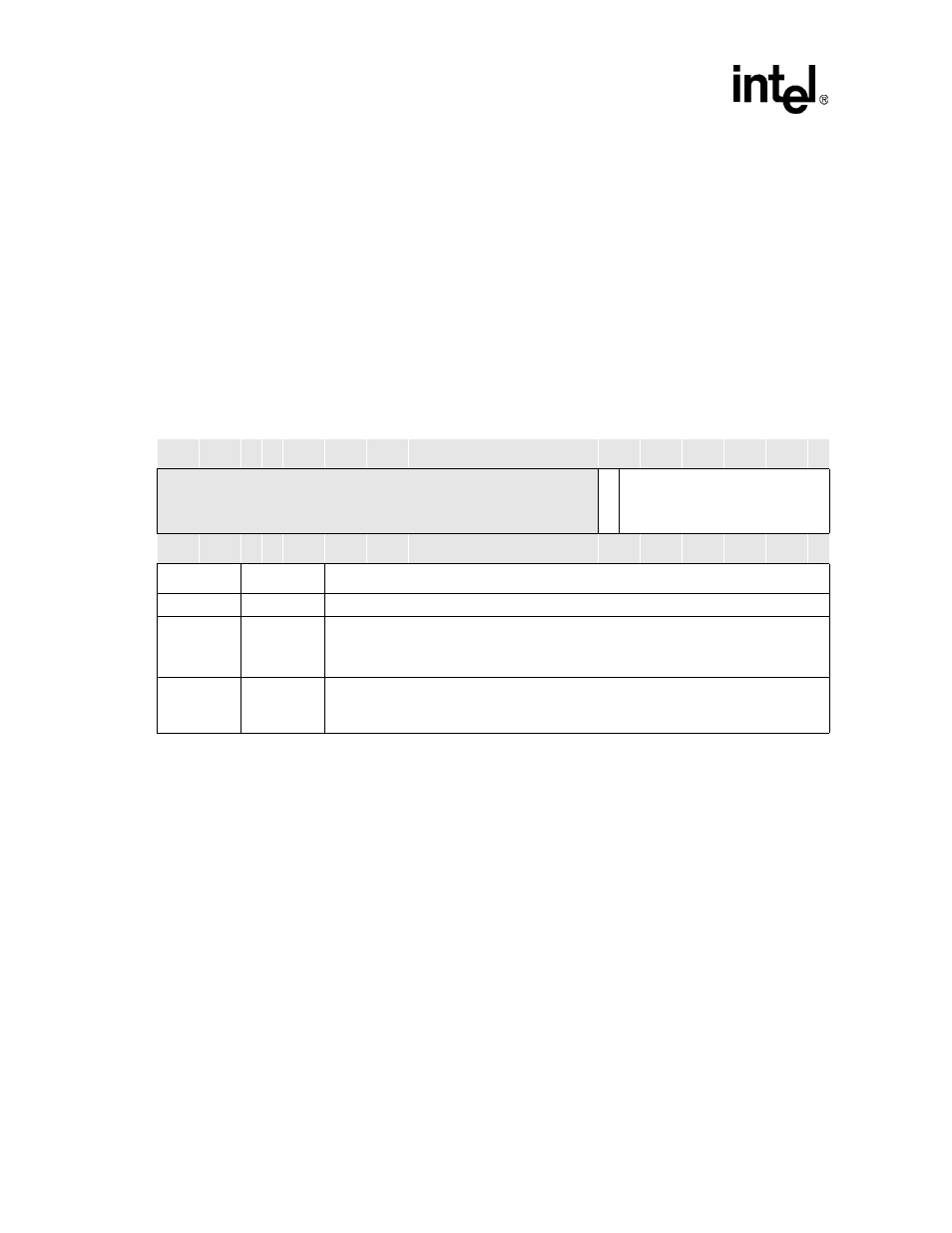

Table 4-51. PWM_DUTYn Bit Definitions

Physical Address

0x40B0_0004

0x40C0_0004

PWM Duty Cycle Registers

(PWM_DUTY0, PWM_DUTY1)

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Reserved

F

D

CY

CL

E

DCYCLE

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

<31:11>

—

Reserved

<10>

FDCYCLE

PWMn FULL DUTY CYCLE:

0 – PWM clock (PWM_OUTn) duty cycle is determined by DCYCLE field.

1 – PWM_OUTn is set high and does not toggle.

<9:0>

DCYCLE

PWMn DUTY CYCLE:

Duty cycle of PWMn clock, i.e. the number of PSCLK_PWM cycles PWMn is asserted

within one cycle of PWMn.