1 tmed energy distribution select (ted), 2 tmed horizontal beat suppression (thbs), 3 tmed vertical beat suppression (tvbs) – Intel PXA26X User Manual

Page 316

7-48

Intel® PXA26x Processor Family Developer’s Manual

Liquid Crystal Display Controller

7.6.10.1

TMED Energy Distribution Select (TED)

TED selects which matrix is used in the final step of TMED algorithm. TMED=1 selects the

(preferred) TMED2 matrix. TMED=0 selects the older TMED matrix. After the pixel value has

gone through the algorithm to determine a lower and upper boundary, the row and column counters

are combined and run through one of the matrices to obtain a number that is compared to the 2

boundaries. If that number is between the 2 boundaries, then the pixel data out in this frame is a 1,

otherwise it is a 0.

7.6.10.2

TMED Horizontal Beat Suppression (THBS)

This is the column shift value used as an offset that is combined with the row (line) counter and the

pixel counter to create an address to lookup in the matrix. The matrix output is compared to the

upper and lower boundaries defined in Section 7.3.3.

7.6.10.3

TMED Vertical Beat Suppression (TVBS)

This is the block shift value used as an offset that is combined with the pixel counter.

7:4

TVBS

TMED VERTICAL BEAT SUPPRESSION:

Specifies the block shift value.

3

FNAME

TMED FRAME NUMBER ADJUSTER ENABLE:

0 – Disable frame number adjuster.

1 – Enable frame number adjuster.

2

COAE

TMED COLOR OFFSET ADJUSTER ENABLE:

0 – Disable color offset adjuster.

1 – Enable color offset adjuster.

1

FNAM

TMED FRAME NUMBER ADJUSTER MATRIX:

0 – Selects Matrix 1 for frame number adjuster.

1 – Selects Matrix 2 for frame number adjuster.

0

COAM

TMED COLOR OFFSET ADJUSTER MATRIX:

0 – Selects Matrix 1 for color offset adjuster.

1 – Selects Matrix 2 for color offset adjuster.

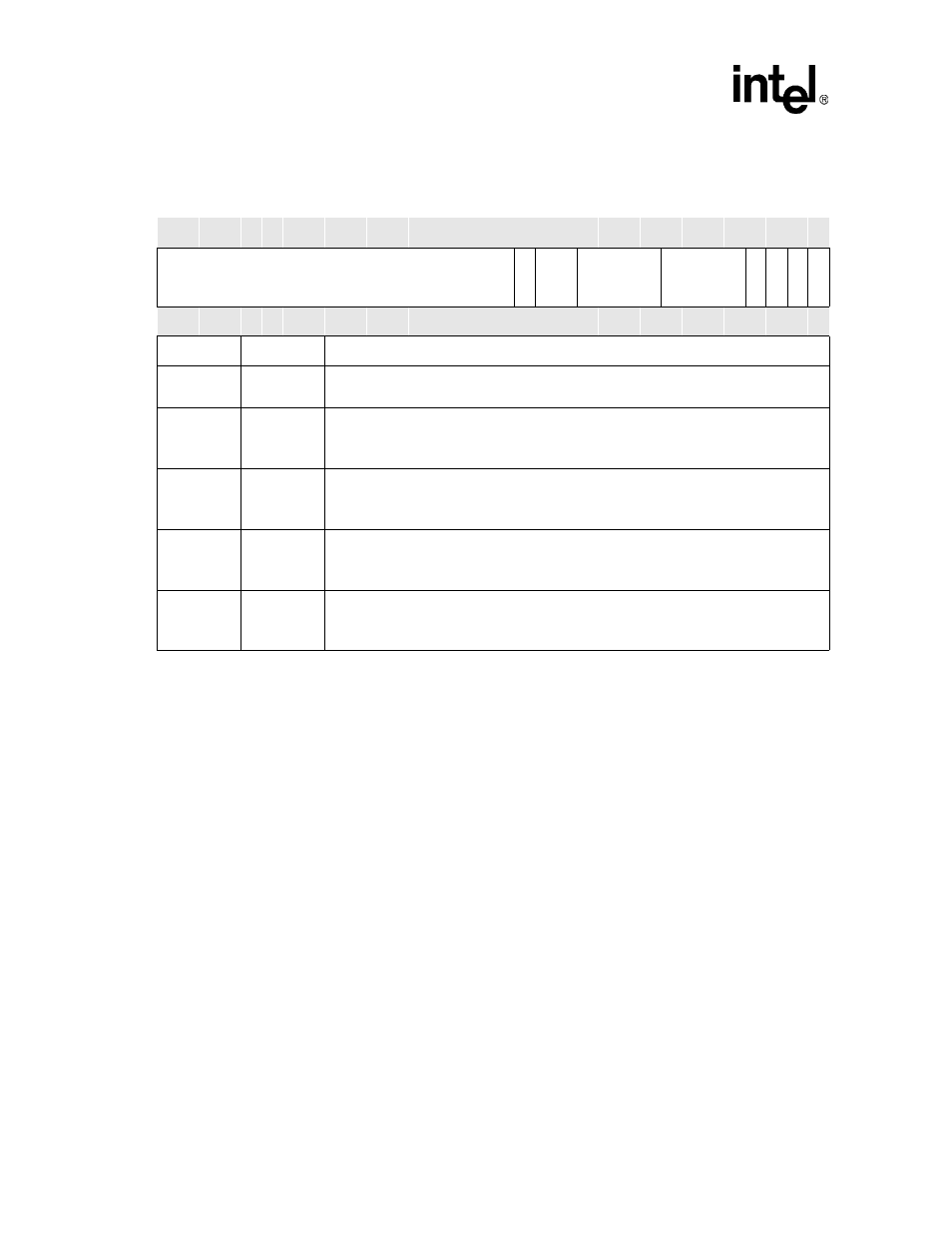

Table 7-15. TMED Control Register (Sheet 2 of 2)

Physical Address

0X4400_0044

TMED Control Register

LCD Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

TED

re

s

e

rved

THBS

TVBS

FN

A

M

E

COA

E

FN

A

M

CO

AM

Reset

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

1

1

1

0

1

0

1

0

1

0

0

1

1

1

1

Bits

Name

Description