Table 12-26. udc endpoint 0 data register – Intel PXA26X User Manual

Page 457

Intel® PXA26x Processor Family Developer’s Manual

12-47

Universal Serial Bus Device Controller

12.6.16

UDC Data Register x (UDDRx), Where x is 1, 6, or 11

Endpoint(x) is a double-buffered bulk IN endpoint that is 64 bytes deep. Data can be loaded via

DMA or direct core writes. Because it is double buffered, up to two packets of data may be loaded

for transmission.

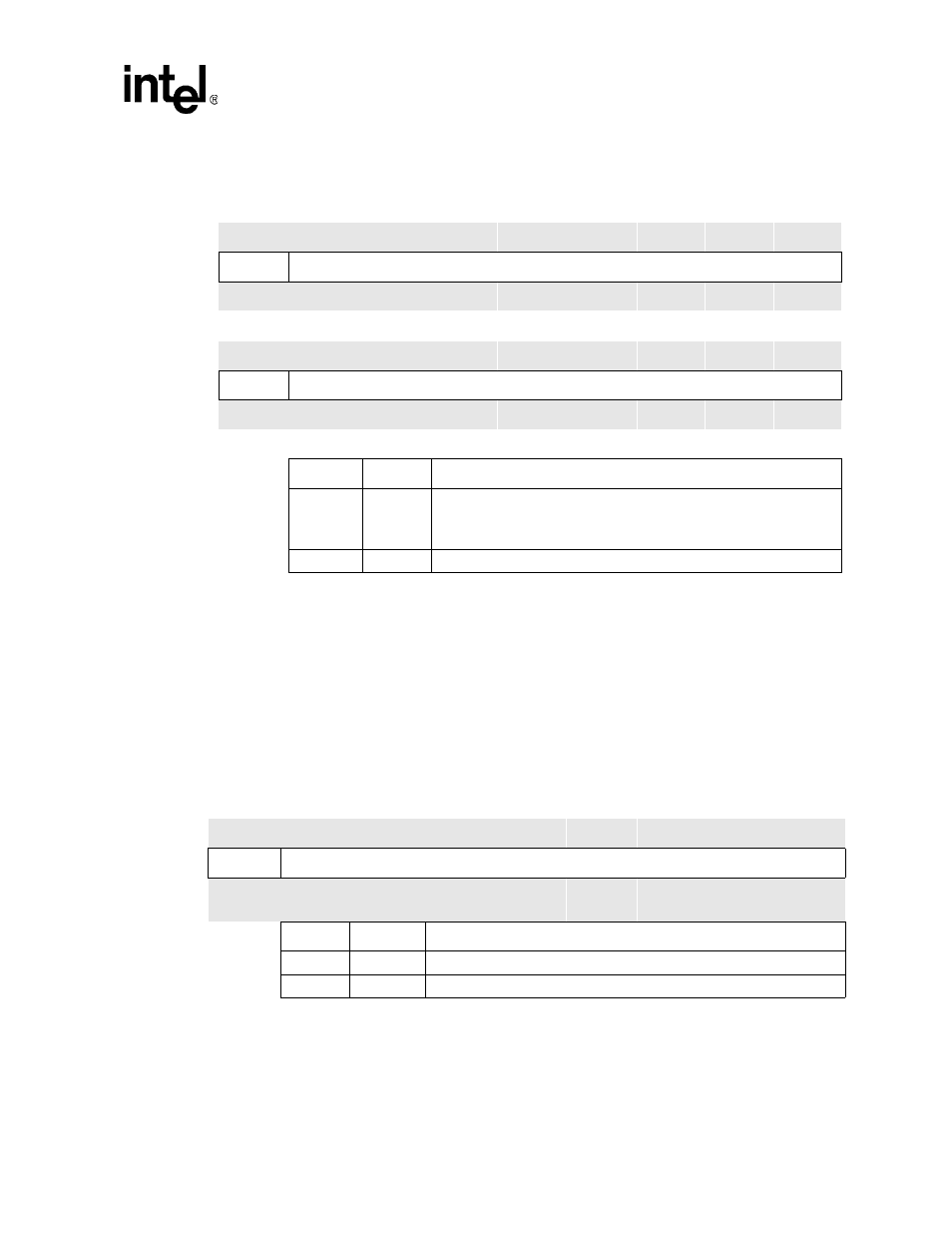

Table 12-26. UDC Endpoint 0 Data Register

0h 4060 0080

UDDR0

Read/Write

Bit

31:8

7

6

5

4

3

2

1

0

Reserved

Bottom of Endpoint 0 FIFO (for Reads)

Reset

X

0

0

0

0

0

0

0

0

31:8

7

6

5

4

3

2

1

0

Reserved

Top of Endpoint 0 FIFO (for Writes)

Reset

X

0

0

0

0

0

0

0

0

Bits

Name

Description

7:0

DATA

Top/bottom of endpoint 0 FIFO data

Read – Bottom of endpoint 0 FIFO data.

Write – Top of endpoint 0 FIFO data.

31:8

—

Reserved for future use

Table 12-27. UDC Endpoint x Data Register, Where x is 1, 6, or 11

0h 4060 0100

UDDR1

Write

0h 4060 0600

UDDR6

Write

0h 4060 0B00

UDDR11

Write

Bit

31:8

7

6

5

4

3

2

1

0

Reserved

8-Bit Data

Rese

t

X

0

0

0

0

0

0

0

0

Bits

Name

Description

7:0

DATA

Top of endpoint data currently being loaded

31:8

—

Reserved for future use