Table 10-15. modem status register - msr – Intel PXA26X User Manual

Page 386

10-20

Intel® PXA26x Processor Family Developer’s Manual

Universal Asynchronous Receiver/Transmitter

Note:

When bit 0, 1, 2, or 3 is set, a modem status interrupt is generated if IER[MIE] is set.

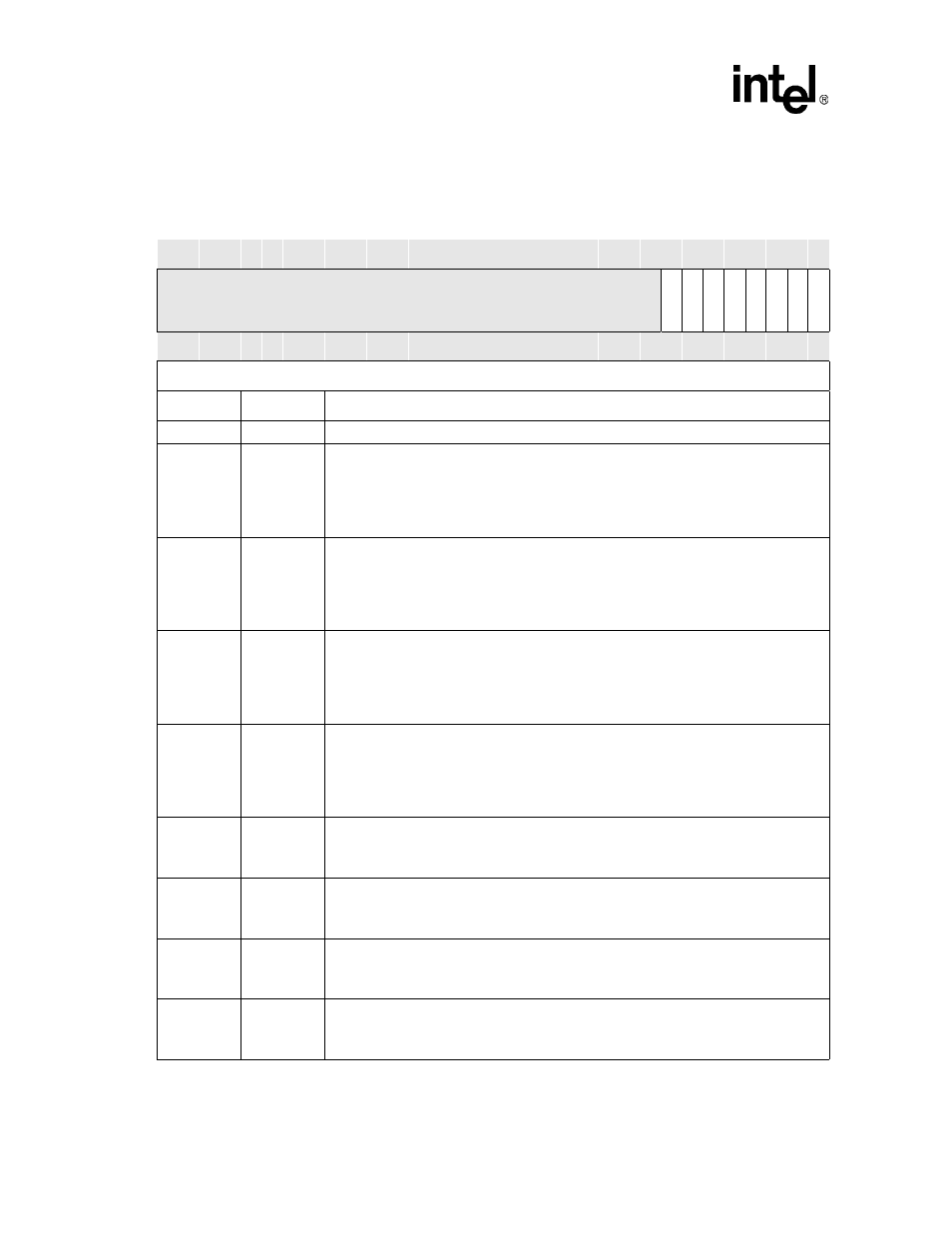

Table 10-15. Modem Status Register

–

MSR

Base+0x18

Modem Status Register

UART

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

R

eser

ved

DC

D

RI

DS

R

CT

S

DDC

D

TER

I

DD

SR

DC

T

S

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Read only

Bits

Name

Description

31:8

—

Reserved

7

DCD

DATA CARRIER DETECT:

Complement of the Data Carrier Detect (nDCD) input. Equivalent to MCR[OUT2] if

MCR[LOOP] is set.

0 – nDCD pin is 1

1 – nDCD pin is 0

6

RI

RING INDICATOR:

Complement of the Ring Indicator (nRI) input. Equivalent to MCR[OUT1] if MCR[LOOP] is

set.

0 – nRI pin is 1

1 – nRI pin is 0

5

DSR

DATA SET READY:

Complement of the Data Set Ready (nDSR) input. Equivalent to MCR[DTR] if MCR[LOOP]

is set.

0 – nDSR pin is 1

1 – nDSR pin is 0

4

CTS

CLEAR TO SEND:

Complement of the Clear to Send (nCTS) input. Equivalent to MCR[RTS] if MCR[LOOP] is

set.

0 – nCTS pin is 1

1 – nCTS pin is 0

3

DDCD

DELTA DATA CARRIER DETECT:

0 – No change in nDCD pin since last read of MSR

1 – nDCD pin has changed state

2

TERI

TRAILING EDGE RING INDICATOR:

0 – nRI pin has not changed from 0 to 1 since last read of MSR

1 – nRI pin has changed from 0 to 1

1

DDSR

DELTA DATA SET READY:

0 – No change in nDSR pin since last read of MSR

1 – nDSR pin has changed state

0

DCTS

DELTA CLEAR TO SEND:

0 – No change in nCTS pin since last read of MSR

1 – nCTS pin has changed state