Table 15-17. mmc_i_reg register, 13 mmc_cmd register – Intel PXA26X User Manual

Page 543

Intel® PXA26x Processor Family Developer’s Manual

15-31

MultiMediaCard Controller

15.5.13

MMC_CMD Register

The MMC_CMD register specifies the command number (see

).

Command index values are shown in (

).

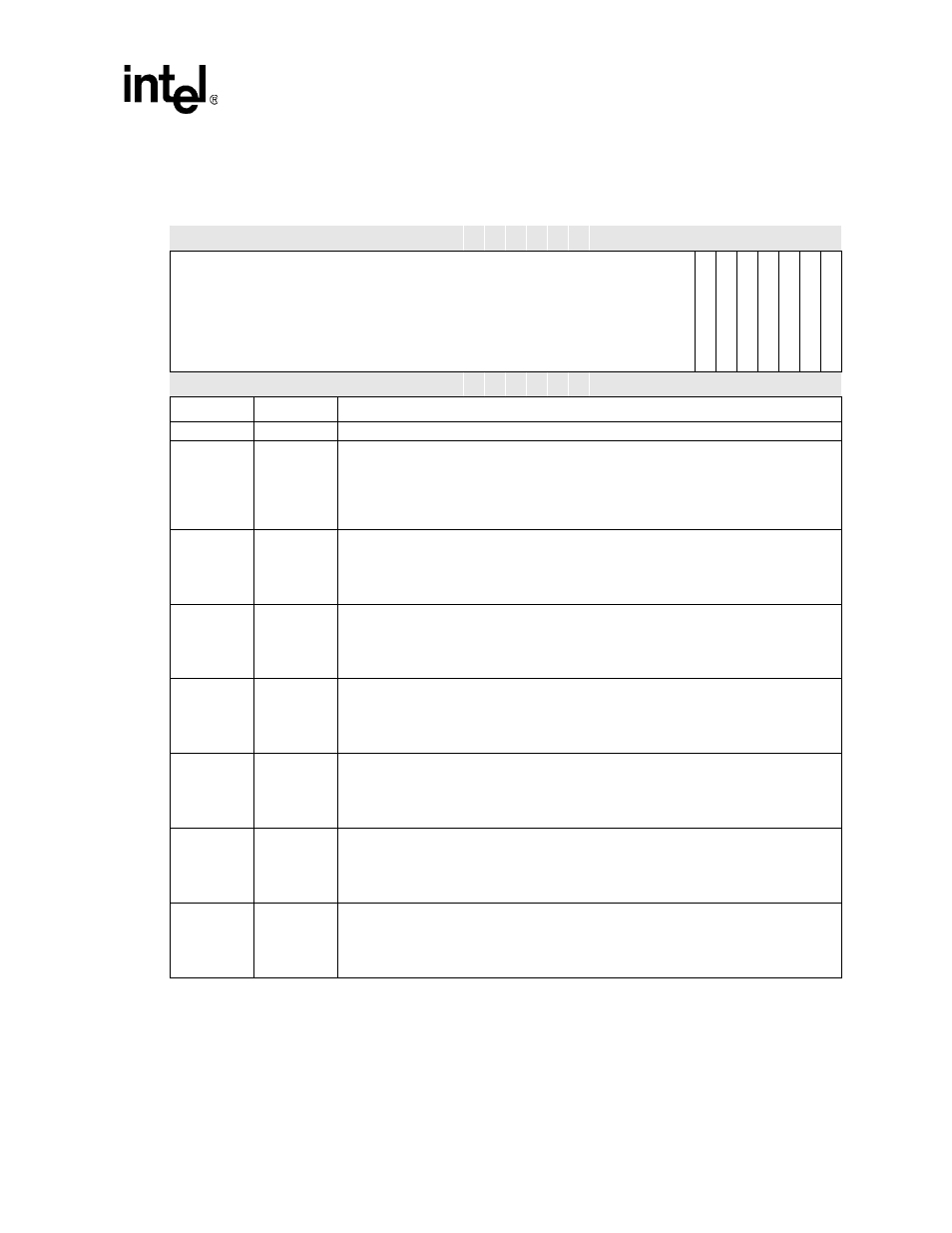

Table 15-17. MMC_I_REG Register

Physical Address

4110_002c

MMC_I_REG Register

MMC

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

R

ese

rved

TX

FIFO

_

W

R

_

R

E

Q

RXF

IF

O

_

R

D_

RE

Q

CL

K

_

IS

_

O

F

F

ST

O

P

_

C

M

D

EN

D_

C

M

D

_

RE

S

P

R

G

_

DO

NE

D

A

T

A

_

T

RA

N_

DON

E

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

31:5

—

Reserved

6

TXFIFO_WR_

REQ

TRANSMIT FIFO WRITE REQUEST:

0 – No Request for data write to MMC_TXFIFO FIFO

1 – Request for data write to MMC_TXFIFO FIFO

Cleared after each write but immediately set again unless there are no entries left in the

FIFIO.

5

RXFIFO_RD_

REQ

RECEIVE FIFO READ REQUEST:

0 – No Request for data read from MMC_RXFIFO FIFO

1 – Request for data read from MMC_RXFIFO FIFO

Cleared after each read but immediately set again unless the FIFO is empty.

4

CLK_IS_

OFF

CLOCK IS OFF:

0 – MMC clock has not been turned off

1 – MMC clock has been turned off, due to stop bit in STRP_CLK register

Cleared by the MMC_STAT[CLK_EN] bit when the clock is started.

3

STOP_CMD

FOR STREAM MODE WRITES:

0 – MMC is not ready for the stop transmission command

1 – MMC is ready for the stop transmission command

Cleared when CMD12 is loaded in the MMC_CMD register and the clock is started.

2

END_CMD_R

ES

END COMMAND RESPONSE:

0 – MMC has not received the response

1 – MMC has received the response or a response time-out has occurred

Cleared by the MMC_STAT[END_CMD_RES] bit.

1

PRG_DONE

PROGRAMMING DONE:

0 – Card has not finished programming and is busy

1 – Card has finished programming and is no longer busy

Cleared by the MMC_STAT[PRG_DONE] bit.

0

DATA_TRAN_

DONE

DATA TRANSFER DONE:

0 – Data transfer is not complete

1 – Data transfer has completed or a read data time-out has occurred

Cleared by the MMC_STAT[DATA_TRAN_DONE] bit.