4 uart operational description, Figure 10-1. example uart data frame – Intel PXA26X User Manual

Page 370

10-4

Intel® PXA26x Processor Family Developer’s Manual

Universal Asynchronous Receiver/Transmitter

10.4

UART Operational Description

shows the format of a UART data frame.

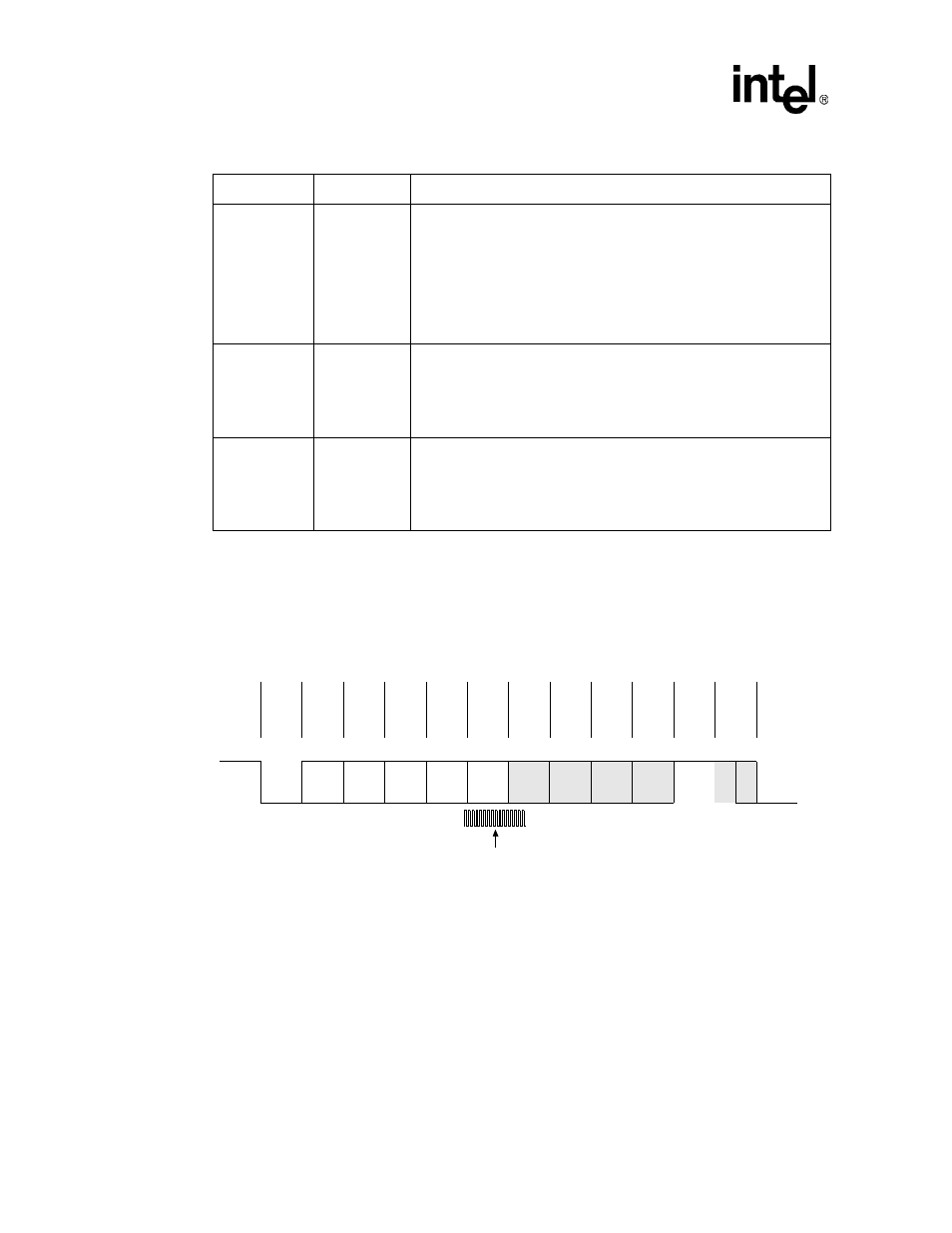

Figure 10-1. Example UART Data Frame

Receive data sample counter frequency is 16 times the value of the bit frequency. The 16X clock is

created by the baud rate generator. Each bit is sampled three times in the middle. Shaded bits in

are optional and can be programmed by software.

Each data frame is between seven and 12 bits long, depending on the size of the data programmed,

whether parity is enabled, and the number of stop bits. A data frame begins by transmitting a start

bit that is represented by a high to low transition. The start bit is followed by from five to eight bits

of data that begin with the least significant bit (LSB). The data bits are followed by an optional

parity bit. The parity bit is set if even parity is enabled and the data byte has an odd number of ones

or if odd parity is enabled and the data byte has an even number of ones. The data frame ends with

one, one and a half or two stop bits, as programmed by software. The stop bits are represented by

one, one and a half, or two successive bit periods of a logic one.

nRI

Input

RING INDICATOR – When low, indicates that the modem or data set has

received a telephone ringing signal. The nRI signal is a Modem Status

input whose condition can be tested by reading Bit 6 (RI) of the MSR. Bit 6

is the complement of the nRI signal. Bit 2, the trailing edge of ring indicator

(TERI), of the MSR indicates whether the nRI input signal has changed

from low to high since the MSR was last read. This signal is only present

on the FFUART.

When the RI bit of the MSR changes from a high to low state and the

Modem Status interrupt is enabled, an interrupt is generated.

nDTR

Output

DATA TERMINAL READY – When low, signals the modem or the data set

that the UART is ready to establish a communications link. The nDTR

output signal can be set to an active low by programming Bit 0 (DTR) of

the MSR to a 1. A Reset operation sets this signal to its inactive state.

LOOP mode operation holds this signal in its inactive state. This signal is

only present on the FFUART.

nRTS

Output

REQUEST TO SEND – When low, signals the modem or the data set that

the UART is ready to exchange data. The nRTS output signal can be set to

an active low by programming Bit 1 (RTS) of the Modem Control Register

to a 1. A Reset operation sets this signal to its inactive (high) state. LOOP

mode operation holds this signal in its inactive state. This signal is used by

the FFUART and BTUART.

Table 10-1. UART Signal Descriptions (Sheet 2 of 2)

Name

Type

Description

Start

Bit

Data

<0>

Data

<1>

Data

<2>

Data

<3>

Data

<4>

Data

<5>

Data

<6>

Data

<7>

Parit

y

Bit

Stop

Bit 1

Stop

Bit 2

TXD or RXD pin

LSB

MSB